#### Chapter

# 10

## Thermal Management Materials and Systems

#### Al Krum

Huntington Beach, California

#### **10.1 Introduction**

Heat is an unavoidable by-product of every electronic device and circuit,<sup>1</sup> and it needs to be minimized to improve reliability and maximize electrical performance. Managing this heat, commonly referred to as *thermal management*, requires an understanding of thermodynamics and an in-depth knowledge of the materials.

This chapter, which provides both an introduction into thermal management of electronic packaging and descriptions of the various materials used, is intended not only for thermal management experts but also for those in related fields who have a need to model and optimize their physical designs.

The trend in electronic packaging has been to reduce size and increase performance. This can be seen in the higher levels of integration in semiconductors and the increased usage of hybrids and multichip modules (MCMs). Intel's first microprocessor, the 4004, had 2,300 transistors. The latest microprocessor, the Pentium 4<sup>\*</sup>, has 42 million transistors.<sup>2</sup> Placing more functions in a smaller package has resulted in higher heat densities, which mandate that thermal management be given a high priority in design so as to maintain system performance and reliability. As clock rates increase every year, the power dissipated in the semiconductors during switching is increasing at a linear rate, proportional to frequency as shown by the following equation:

<sup>\*</sup> Pentium is a registered trademark of Intel Corporation.

$$P = \frac{CV^2}{2}f \tag{10.1}$$

where C = input capacitance in farads

V = peak-to-peak voltage swing of signal in volts

f = switching frequency in hertz

If the values of input capacitance and voltage swing had remained the same while the clock frequency increased, the amount of power dissipated would have grown at an exponential rate and would be unmanageable. Luckily, the thermal designer has been aided with reduced input capacitance for each new generation of integrated circuits. In addition, voltage swings, which are directly tied to logic power supply voltages, have been undergoing reduction from the classic 5.0 V to a forecast <1 V.<sup>3</sup>

The initial sections of this chapter review basic heat flow theory as applied to electronic packaging. Next, the various packaging methods and their materials are investigated. Finally, the factors that determine thermal resistance are evaluated.

#### 10.1.1 Temperature effects on circuit operation

Increasing the temperature of an active device typically changes its electrical parameters such as gain, leakage, offset, threshold voltage, and forward drop. These parameter variations over temperature are well documented and incorporated into most circuit simulations. Most circuit designers are aware that leakage currents in active silicon devices approximately double every 10°C. Minimizing the temperature of these devices thus reduces the effect of the leakage currents. If the temperature of an active device increases too much, it will exceed the manufacturer's specifications and usually will fail.

Changing the temperature of passive devices typically changes their values. For example, film resistors have temperature coefficients that range from several to several hundred parts per million per degree Celsius (ppm/°C). Ceramic capacitors, depending on the dielectric material, have temperature variations from 30 ppm/°C to 60 percent over the military or extended temperature range (-55 to +125°C). These changes in electrical parameters are typically not desired. If the temperature increase is high enough, the active or passive device being heated may permanently degrade or even totally fail. Such failures include thermal runaway, junction failure, metallization failure, corrosion, resistor drift and electromigration diffusion. Therefore, the electrical designer needs to minimize any temperature increases. While the designer may not have control over environmental changes, he does have control over the device's self-heating. For analog circuits, he can make the circuits as efficient as possible. For digital circuits, he can select devices that produce the lowest amount of heat for the required clock rates.

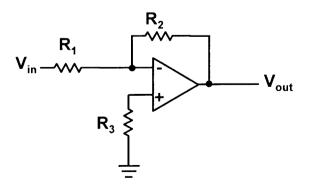

In some hybrid and MCM circuits, certain component pairs or groups are designed to track over temperature to achieve the required circuit performance. Typically, resistors, transistors and diodes are components that fall into this category. For example, in an operational amplifier circuit, as shown in Fig. 10.1, resistors  $R_1$  and  $R_2$  must track to achieve constant gain over temperature. If  $R_1$  were physically located in a cool location on the substrate and separated from  $R_2$ , located next to a power transistor whose power level and thus temperature were varying, then the output of the operational amplifier  $V_{out}$  would modulate as a function of temperature and power in the transistor. One solution would be to relocate  $R_2$  adjacent to  $R_1$  and isolate it from the power transistor so that it would have less heating effect on  $R_2$ . Techniques to achieve this latter solution include using a larger power transistor, a better thermal die attach, a heat spreader, or a better substrate-to-package attach.

Therefore, to meet both the electrical and thermal performance of a circuit, the designer must thermally and electrically model each device and iterate the design to achieve the required performance. If any devices that must closely track are found to have significant differences, then the physical designer must either select alternate materials or incorporate additional cooling schemes.

#### 10.1.2 Temperature effects on physical construction

With few exceptions, materials expand when their temperature is raised and contract when cooled. The *temperature coefficient of expansion* (TCE) is a parameter found in the literature for each material. Another name for this parameter is the *coefficient of thermal expansion* (CTE). The CTEs and thermal conductivities for various materials used in microelectronic assemblies are detailed in subsequent tables.

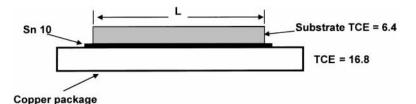

Thermal stresses occur when a material is constrained during expansion or contraction. An example of this is a copper heat sink soldered to a metallized ceramic substrate as shown in Fig. 10.2. The ceramic has a CTE of 6.4 ppm/°C, whereas the copper has a CTE of 16.8 ppm/°C. During temperature cycling, in which there are a number of periods of heating followed by cooling periods, the copper expands and then contracts at a higher rate than the ceramic but is

Figure 10.1 Gain tracking of resistors  $R_1$  and  $R_2$ .

Figure 10.2 Stress example.

constrained. This constraining could result, after time and repeated temperature cycles, in the heat sink bending, the solder joint failing, the ceramic warping, or the ceramic completely failing and cracking.<sup>3</sup> To reduce or eliminate the thermal stresses requires both a selection of the correct materials and a minimization of the temperature changes caused by self-heating.

#### 10.2 Understanding of Thermal Management

#### 10.2.1 Second law of thermodynamics

The second law of thermodynamics states that heat always flows spontaneously from a hotter region to a cooler region as shown in Fig. 10.3. All active and passive devices are sources of heat. These devices are always hotter than the average temperature of their immediate surroundings.

#### 10.2.2 Heat transfer mechanisms

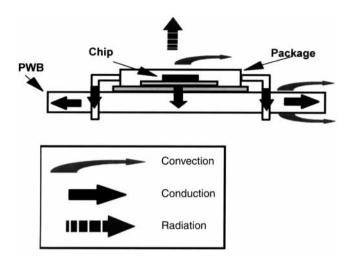

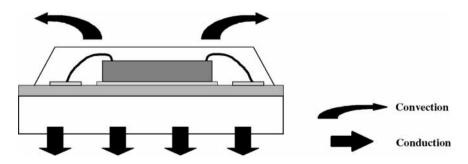

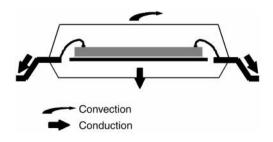

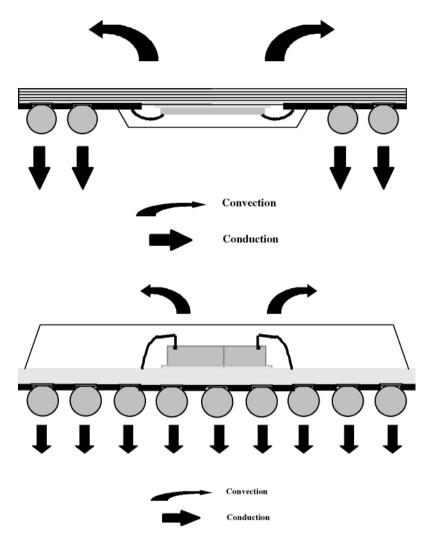

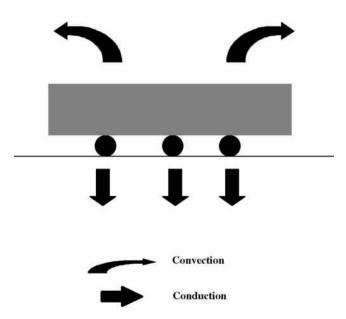

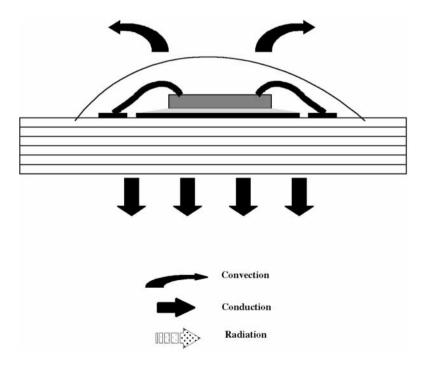

There are three mechanisms for heat transfer: conduction, convection, and radiation, as depicted in Fig. 10.4. These mechanisms and the temperature distribution from the heat source to the surroundings will be discussed in the following sections.

**10.2.2.1 Conduction.** Thermal conduction is a process in which heat flows through a solid, liquid, or gas or between two media that are in intimate contact. Conduction, the dominant mechanism for heat transfer within solids, involves the transfer of kinetic thermal energy from one electron to another, causing no visible motion of the particles of the body. Conduction through dielectric solids is almost entirely a result of lattice vibrations, whereas conduction through metallic solids has the added energy transport by free electrons. This thermal energy transfer via electrons is similar to that of an electrical

Figure 10.3 Second law of thermodynamics.

Figure 10.4 Mechanisms of heat transfer.

charge. It is not surprising to find that good electrical conductors such as copper and silver are good thermal conductors.

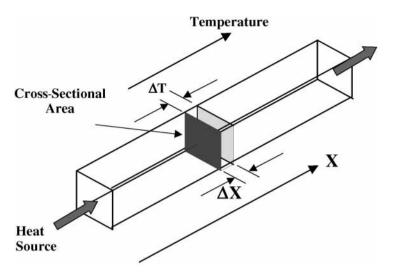

**Fourier's law**. Fourier's law of heat conduction, named after the French mathematician, Jean Fourier, states that the rate of heat flow equals the product of the area normal to the heat flow path, the temperature gradient along the path, and the thermal conductivity of the medium. Mathematically, Fourier's law can be expressed as

$$\frac{dq}{dt} = -KA\frac{dT}{dX} \tag{10.2}$$

where K = thermal conductivity of medium, W/m-K or W/in-°C

- A = cross-sectional area of medium normal to the heat flow path, in<sup>2</sup> or cm<sup>2</sup>

- T =temperature of medium, °C

- X = position along the medium, in or cm

- t = time, sec

- q = heat generated per unit volume, joules/cm<sup>3</sup>

- Q = heat flow in watts normal to the cross-sectional area of heat transfer

$$\frac{dQ}{dt} = p \text{ ower in W or cal/sec}$$

(10.3)

$$\frac{dt}{dX} = \text{temperature gradient in °C/in or °C/cm}$$

(10.4)

The temperature gradient and the cross-sectional area are defined at the same point X as shown in Fig. 10.5. Heat flow is considered positive when the

Figure 10.5 Fourier's law of heat conduction.

temperature is decreasing. The thermal conductivity of many materials varies with temperature and will be discussed in subsequent sections. In most cases, this variation with temperature can be considered a second-order effect and contributes only a minor source of error.

Substituting Eq. (10.3) into Eq. (10.2) and rearranging gives the expressions

$$P\,dX = KA\,dT\tag{10.5}$$

$$P\int_{0}^{X} dX = KA \int_{T_{2}}^{T_{1}} dT$$

(10.6)

Integrating the above over the length from 0 to X, and from the corresponding temperatures  $T_2$  to  $T_1$ , the equation reduces to

$$PX = KA\Delta T \tag{10.7}$$

Rewriting Eq. (10.7) produces an expression for temperature difference,

$$\Delta T = \frac{PX}{KA} \tag{10.8}$$

The Greek letter theta ( $\theta$ ) is usually used to symbolize thermal resistance and can be mathematically defined using Eq. (10.9).

$$\theta = \frac{X}{KA} \tag{10.9}$$

Combining Eqs. (10.8) and (10.9) gives a relationship between thermal resistance, power, and temperature rise.

$$P\theta = \Delta T \tag{10.10}$$

**10.2.2.2 Convection.** Convection is the transfer of thermal energy between two surfaces as a consequence of a relative velocity between them.<sup>4</sup> It occurs only in fluids wherein the transfer mechanism is the mixing of the fluids. Although each of the surfaces may be a fluid, the most practical application is where one is a solid surface and the other is a fluid.

The heat loss due to Newtonian cooling (named after Sir Isaac Newton) or convection cooling is proportional to the temperature difference between them. In mathematical terms, this can be written as

$$Q_c = h_c A_s (T_s - T_A) = h_c A_s \Delta T \tag{10.11}$$

where  $Q_c$  = heat transferred from a surface to ambient by convection in watts  $A_s$  = surface area in cm<sup>3</sup> or in<sup>3</sup>

- $T_{\circ}^{\circ}$  = surface temperature in °C

- $T_A^{\circ}$  = ambient temperature in °C (temperature to which the heat is being transferred)

- $h_c$  = convection heat transfer coefficient in W/cm<sup>3</sup>-°C or W/in<sup>3</sup>-°C

Because  $h_c$  is both position and temperature dependent, convection heat transfer solutions are more complex than conduction solutions. Many analysts use a simplifying approximation in which the average surface temperature is used in conjunction with an average heat transfer coefficient,  $h_c$ .

Equation (10.11) can be rewritten as:

$$\Delta T = \frac{1}{h_c A_s} Q_c \tag{10.12}$$

The term  $\theta_S$  can be defined as the convective surface thermal resistance.

$$\theta_S = \frac{1}{h_c A_s} \tag{10.13}$$

It should be noted that Eq. (10.13) is not a law of heat transfer as seen in Fourier's law but is a definition of the heat transfer coefficient. This definition simply states the quantity of heat transferred through a temperature difference. This temperature coefficient actually depends on the surface and surrounding temperatures, fluid velocity (for forced convection), fluid viscosity, fluid density, and surface geometry.

There are two types of convection cooling: natural (or free) and forced. In natural convection cooling, heat flows by conduction or contact from the surface to the fluid particles in intimate contact with the surface. The fluid particles increase in internal energy, causing the density of the nearby fluid to decrease. Buoyant forces then cause the particles to move to a region lower in temperature where further energy transfer takes place by conduction. There is a resulting boundary layer of hot air immediately adjacent to the surface. Natural convection is caused entirely by differences in density within the fluids resulting from different temperatures and does not use externally forced air movement.

In forced convection, the thermal energy is transferred from the solid to the adjacent fluid particles in the same manner as in natural convection. However, the subsequent fluid action occurs through artificially induced fluid motion generated by fans, pumps, or blowers. There are three types of air-moving devices: centrifugal, propeller, and axial flow. Centrifugal fans are designed to move small volumes of air at high velocities and are capable of working against a high resistance. Propeller types are designed to move large volumes of air at low velocities. Axial flow fans are an intermediate type of air mover between the centrifugal and propeller types.

Forced convection can be divided into laminar flow and turbulent flow. For air, the transition from laminar to turbulent flow usually occurs at a velocity of 180 linear feet per minute (LFM). The heat is transferred by molecular conduction in the fluid and by the solid—fluid interface. Turbulent flow, characterized by the irregular motion of fluid particles, has eddies in the fluid in which the particles are continuously mixed and rearranged. The heat is transferred from the eddies back and forth across the streamlines. The greater heat transfer occurs for turbulent flow.

For forced convection, the convection heat transfer coefficient is calculated from

$$h = B \frac{V^{0.75}}{L^{0.25}} \tag{10.14}$$

where B = constant of air properties and surface configuration

*V* = linear velocity of air in cm/sec or in/sec

L = characteristic length of surface in direction of flow in cm or inch

As can be seen in Eq. (10.14), the linear velocity of the air current as it passes the dissipating element is the key factor to the amount of heat that can be removed.

For natural or free convection, the convection heat transfer coefficient is calculated by

$$h = DE \frac{\Delta T^{0.25}}{L^{0.25}} \tag{10.15}$$

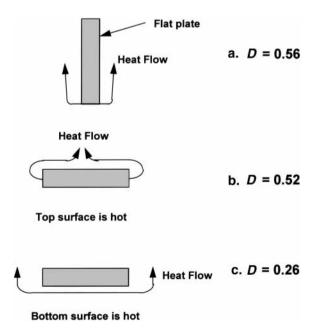

where D = constant for air properties (see Fig. 10.6) E = constant for surface configuration ( $E = 1.9 \times 10^{-4}$  for a flat plate)

- L = characteristic length in centimeters or inches of dissipator surface with area factor

- $\Delta T$  = temperature difference in °C between dissipator and ambient air

10.2.2.2.1 Natural convection cooling example. A flat plate with a characteristic length of 2.0 in (assumed value for this example), shown in Fig. 10.6c, can be considered to be a model for a flat heat sink. The plate size is  $2.0 \times 2.0$  in. The plate bottom is at 125°C, and the ambient air is 25°C. The value of D for this configuration is 0.26 (from Fig. 10.6c). Calculating the value of the convective transfer heat coefficient  $h_c$ , from Eq. (10.15),

$$h_c = DE \frac{\Delta T^{0.25}}{L70.25} = 0.26 \times 1.9 \times 10^{-4} \frac{(125 - 25)^{0.25}}{20^{0.25}} = 1.31 \times 10^{-2}$$

The convection surface thermal resistance is

$$\theta_s = \frac{1}{h_c A_s} = \frac{1}{1.31 \times 10^{-2} \times 4} = 1.9^{\circ} \text{C/W}$$

(10.16)

**10.2.2.2.2 Forced convection example.** Air with a velocity, *V*, of 500 ft/min is blown across a plate with a characteristic length *L* of 2.0 in. The surface area *A* is 4.0 in<sup>2</sup>, and the air property/surface configuration constant *B* is  $1.0 \times 10^{-3}$ . From Eq. (10.14),

**Figure 10.6** Value of D in Eq. (10.15).

$$h = B \frac{V^{0.75}}{L^{0.25}} = 1.0 \times 10^{-3} \frac{(500 \times 12)^{0.75}}{2^{0.25}} = 0.482 \text{ W/in}^{2} \text{-}^{\circ}\text{C}$$

(10.17)

The thermal resistance is

$$\theta_s = \frac{1}{hA_S} = \frac{1}{0.482 \times 4} = 0.518^{\circ} \text{C/W}$$

(10.18)

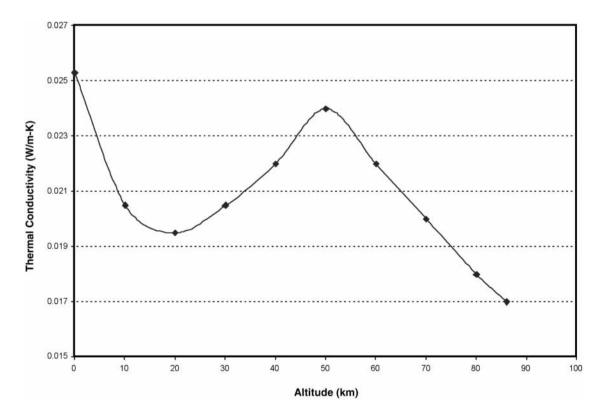

The above discussion of convection cooling points out that this heat removal method is wholly dependent on the movement of the fluid surrounding the heat-dissipating element. A brief review of the thermal conductivities of the various gases present in packaging will be presented. Because this chapter delves only into thermal management materials, there will be no further discussion of convection cooling.

**10.2.2.3 Radiation cooling.** All objects with a temperature above 0 kelvins emit thermal radiation. Radiation cooling is the transfer of heat by electromagnetic emission, primarily in the infrared wavelengths (0.1 to 100  $\mu$ m). Because radiation cooling does not require a transport medium, it is the only means of cooling in a complete vacuum. Specifically, radiation cooling is maximized when there is no intervening material.

Radiation from solid objects may be considered to be a totally surface-related phenomenon that is electromagnetic in character.

Temperature radiators can be broken into two classes: *black bodies* and *non-black bodies*. Non-black bodies can be further broken down into gray bodies and selective radiators. A visibly black surface absorbs all visible light that falls upon it. Its thermal analogy is called a black body and is defined as a surface that absorbs the entire thermal radiation incident upon it, neither reflecting nor transmitting any of the incident radiation. The emissive power of a black body or surface is defined as  $E_b$ . Good absorbing materials are also good emitting materials. The black body, at any given temperature, radiates more energy, both in the total spectrum and for each wavelength interval, than any other temperature radiator and more than any non-black body at the same temperature.<sup>6</sup>

Real surfaces do not radiate precisely as described by black-body equations, because no surface is ideally black. Lampblack and some finely divided metals approach a black body in certain parts of the spectrum. The actual monochromatic emissive power of a real surface is always less than  $E_b$ . The emissivity of a body or surface ( $\epsilon$ ) is defined as the ratio of the radiated flux (E) emitted by a body to that ( $E_b$ ) emitted by a black body at the same temperature.

$$\varepsilon = \frac{E}{E_b} \tag{10.19}$$

A black body or perfect emitter would have an  $\epsilon$  of 1.0. A perfect reflector would have an  $\epsilon$  of 0. Listed in Table 10.1<sup>5</sup> are the emissivities for various ma-

| Surface type | Finish                                     | Emissivity, ε |

|--------------|--------------------------------------------|---------------|

| Paint        | Black (flat lacquer)                       | 0.96–0.90     |

| Paint        | Gray                                       | 0.84 - 9.91   |

| Paint        | White                                      | 0.80 - 0.91   |

| Paint        | White epoxy                                | 0.91 - 0.95   |

| Paint        | Aluminum silicone                          | 0.020         |

| Metal        | Nickel                                     | 0.21          |

| Metal        | Aluminum                                   | 0.14          |

| Metal        | Silver                                     | 0.10          |

| Metal        | Gold                                       | 0.04 - 0.23   |

|              | Specialty surfaces                         |               |

| Metal        | Aluminum (sandblasted)                     | 0.41          |

| Metal        | Aluminum (black anodized)                  | 0.86          |

| Metal        | Nickel (electrolysis)                      | 0.06 - 0.17   |

| Metal        | Aluminum (machine polished)                | 0.03 - 0.06   |

| Metal        | Gold (electrodeposited or polished)        | 0.02          |

| Ceramic      | Cermet (ceramic containing sintered metal) | 0.58          |

| Metal        | Brass (highly polished)                    | 0.58          |

| Metal        | Copper (polished)                          | 0.018         |

| Metal        | Nickel (polished)                          | 0.070         |

| Metal        | Silver (polished)                          | 0.02 - 0.03   |

| Glass        | Smooth                                     | 0.9 - 0.95    |

| Metal        | Alodine <sup>*</sup> on aluminum           | 0.15          |

| TABLE 10.1 Emissivities of Surfaces at 80°F | TABLE 10.1 | Emissivities of | f Surfaces | at 80° | °F |

|---------------------------------------------|------------|-----------------|------------|--------|----|

|---------------------------------------------|------------|-----------------|------------|--------|----|

\*Registered trademark of Achem Products, Inc.

terials used in microelectronic applications. Aluminum, a low-cost material with a high thermal conductivity, has a low emissivity of 0.04 in a polished state. After black anodization, aluminum's emissivity is significantly increased to 0.80.

A gray body is defined as a radiator that has the same spectral emissivity for all wavelengths. A *selective radiator* is one in which the emissivity varies with wavelength.

The rate of emission of radiant energy from the surface of a body, R, can be expressed by the Stefan-Boltzmann law shown in Eq. (10.20).

$$R = \varepsilon \sigma T^4 \tag{10.20}$$

with R defined as

$$R = \frac{Q}{A} \text{ W/m}^2 \tag{10.21}$$

where  $\varepsilon = \text{surface emissivity in joules/sec-cm}^2$

$\sigma$  = Stefan-Boltzmann constant (3.65 × 10<sup>-11</sup> watts/ in<sup>2</sup>-K<sup>4</sup>)

Q = heat transferred in watts A = radiating surface area in meter<sup>2</sup> T = temperature of surface in kelvins

Combining Eqs. (10.20) and (10.21),

$$Q = \varepsilon \sigma A T^4 \tag{10.22}$$

The heat transferred via radiation between two black body surfaces ( $\varepsilon = 1$ ) in which one body is completely enclosed by the other (and the internal body cannot see any part of itself) may be calculated by

$$Q = A\sigma(T_1^4 - T_2^4)$$

(10.23)

where  $T_1$  = temperature of "hot" body in K  $T_2$  = temperature of "cold" body in K (air molecules or other absorbing body)

For non-black body surfaces, the heat transferred via radiation is

$$Q = SA\varepsilon\sigma(T_1^4 - T_2^4)$$

(10.24)

where S = shielding factor or view factor

The shielding factor (or view factor), S, whose value ranges from 0 to 1, is a measure of how well the emitter sees the absorber. Typical values of shielding factors are shown in Table 10.2.

| Configuration                                                                    | Shielding<br>factor |

|----------------------------------------------------------------------------------|---------------------|

| Infinite parallel plates or planes                                               | 1.0                 |

| Body completely enclosed by another body, internal body cannot see any part of   |                     |

| itself                                                                           | 1.0                 |

| Two squares in perpendicular planes with a common side                           | 0.20                |

| Two equal, parallel squares separated by a distance equal to the side            | 0.19                |

| Two equal, parallel circular disks separated by a distance equal to the diameter | 0.18                |

TABLE 10.2 Shielding Factors for Various Configurations<sup>3</sup>

The above discussion on radiation cooling points out that this heat removal method is dependent on the temperature difference between objects, their emissivity, and the shielding factor. From a materials standpoint, the physical designer can optimize the thermal design with the emissivity parameter. 10.2.2.3.1 Radiation example (non-black body). The bottom of a heat sink is at  $150^{\circ}$ C while the ambient air is at  $25^{\circ}$ C. The heat sink is nickel plated with a surface area of 4.0 in<sup>2</sup>. The shielding factor is 1.0. The amount of heat transferred by radiation is calculated from Eq. (10.24).

$$Q = P = SA\varepsilon\sigma(T_1^4 - T_2^4)$$

= (1)(4)(0.11)(3.65 × 10<sup>-11</sup>)[(150 + 273)<sup>4</sup> - (25 + 273)<sup>4</sup>] = 0.388 W (10.25)

If the heat sink bottom temperature is changed to 125°C, then

$$T_2 = 125^{\circ}\text{C}, \qquad Q = 0.111 \text{ W}$$

#### 10.3 Unit Conversions

Comparisons of the thermal properties of materials is often made difficult by the fact the values use different units. To aid the reader, conversion factors between metric and English units for various physical parameters are listed in Table 10.3.

#### 10.4 Packaging Overview

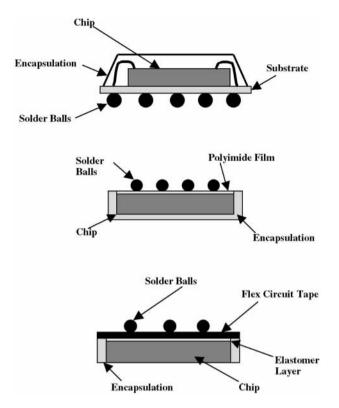

Before looking at the various materials used in electronic packaging from a thermal management standpoint, it is necessary to take a global look at the various packaging technologies and how they fit together. This chapter will look at first-level of packaging—the chip(s) in a package—and the second level of packaging—the circuit card.

Semiconductors are packaged for four basic reasons.

- 1. The package provides mechanical support to the semiconductor.

- 2. The package provides interconnections of the semiconductor(s) to the next level of packaging.

- 3. The package provides environmental protection of the semiconductor(s).

- 4. The package provides a method of removing the heat dissipated by the semiconductor(s).

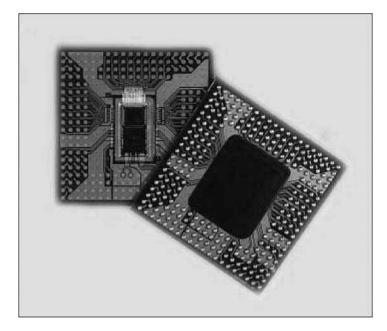

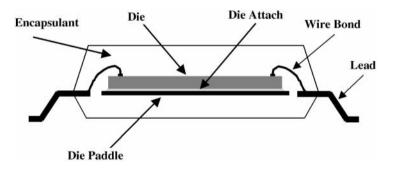

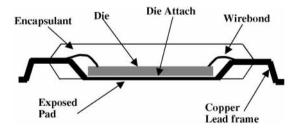

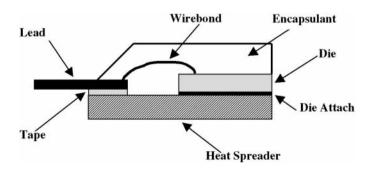

#### 10.4.1 Single-chip package

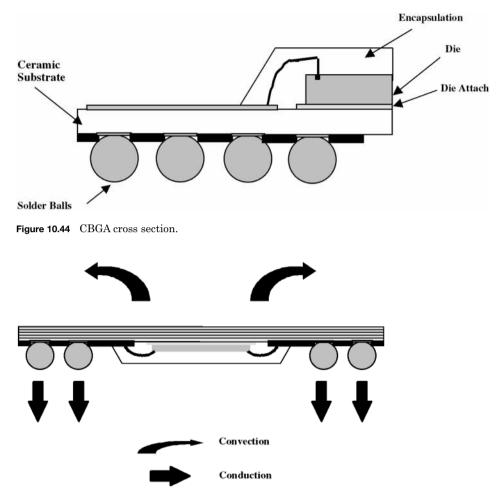

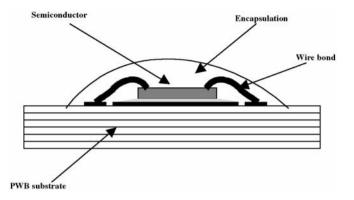

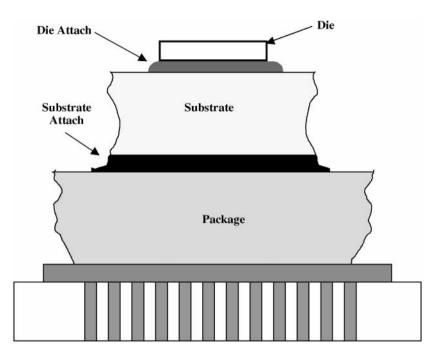

The lowest level of packaging is the single-chip package (SCP). In this package, the chip is mounted to the package base with a die attach material, interconnected, and sealed either hermetically or via encapsulation. An example of the SCP is shown in Fig. 10.7, which depicts a custom ASIC in a ball grid array package. This process is varied for flip-chips wherein the balls on the die are mass reflowed to the package and then sealed.

Figure 10.7 Single-chip package.

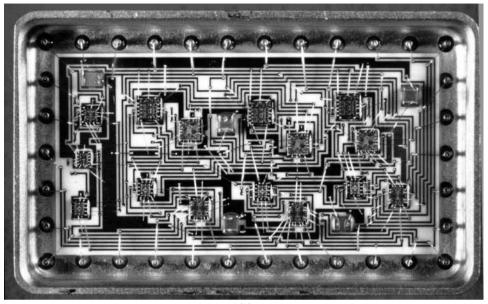

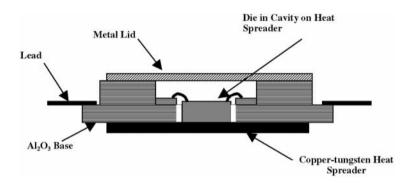

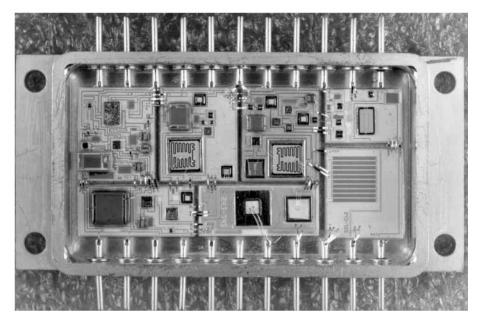

#### 10.4.2 Multichip package

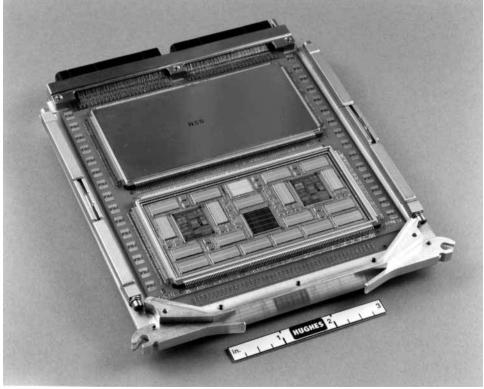

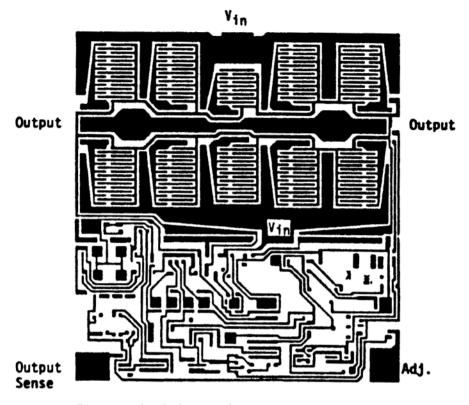

Multichip packaging has been used by the electronics industry since the mid 1960s. First known as hybrids, they placed several semiconductors and passive devices on a substrate housed in one package. The typical package used for the first hybrids was the TO-5. A more recent hybrid is shown in Fig. 10.8a. Over the years, multichip packaging technology has evolved in size, number of I/Os, and complexity to a point at which complete subsystems have been placed in a single package. The highest density of multichip packaging has been named the multichip module (MCM). An example of an MCM with 442 I/Os is shown in Fig. 10.8b. Another name for high-density multichip packaging is *system-in-package* (SiP). A variant of multichip packaging is the *few chip package* (FCP).

#### 10.4.3 Board level

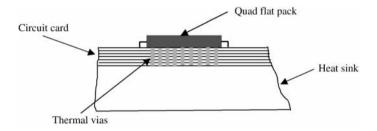

Once the semiconductors are packaged, they need to be attached to the next level of assembly—the circuit card. The electrical interconnections are typically made with a low-temperature solder. For many package types, this electrical connection also acts as the mechanical connection. However, for large devices, additional mechanical attachment is necessary. This may be in the form of adhesives or actual clamping to the circuit card. The additional attachment materials may also aid in removing the heat from the device. Even if the lead attachment is sufficient for holding the package on the circuit card, ther-

(a)

(b)

Figure 10.8 (a) Hybrid microcircuit and (b) multichip modules assembled on SEM-E frame.

| Length, area, and volume                                                  | Work                                               |  |

|---------------------------------------------------------------------------|----------------------------------------------------|--|

| 1 in = 25.4 mm = 0.0254 m                                                 | 1 in-lb (force) = 0.113 J = 0.113 Nm               |  |

| 1 in = 2.54 cm                                                            | 1  ft-lb = 1.365  J                                |  |

| 1 in = 25400 µm (microns)                                                 | 1 BTU = 778 ft-lb = 252 calories = 1,055 J         |  |

| 12  in = 1  ft                                                            | Energy                                             |  |

| 1  ft = 305  mm = 0.305  m                                                | 1 calorie (cal) = 4.186 J                          |  |

| $1~{\rm in}^2\!=\!645~{\rm mm}^2\!=\!0.6452\times 10^{-3}~{\rm m}^2$      | $1 \operatorname{erg} = 10^7 \operatorname{J}$     |  |

| $1 \text{ ft}^2 = 92,880 \text{ mm}^2 = 0.0929 \text{ m}^2$               | 1 electron volt (eV) = $1.60 \times 10^{19}$ joule |  |

| $1 \text{ in}^3 = 16,380 \text{ mm}^3 = 16.38 \times 10^{-6} \text{ m}^3$ | 1  W-sec = 1  J                                    |  |

| $1 \text{ ft}^3 = 0.0283 \text{ m}^3$                                     | Power                                              |  |

| Mass                                                                      | 1 BTU/hr = 0.293 W                                 |  |

| 1 lb (mass) = 0.45359 kg = 453.59 g                                       | 1  cal/sec = 4.18  W                               |  |

| 1 oz = 28.35 g                                                            | 1  ft-lb/sec = 1.356  W                            |  |

| Density                                                                   | 1  ft-lb/mm = 0.0226  W                            |  |

| 1 lb/in <sup>3</sup> = 27680 kg/m <sup>3</sup>                            | Thermal conductivity                               |  |

| $1 \text{ lb/in}^3 = 27.68 \text{ g/m}^3$                                 | 1 BTU/hr-ft-°F = 1.7303 W/m-K                      |  |

| $1 \text{ lb/ft}^3 = 16.0185 \text{ kg/m}^3$                              | 1 BTU/hr-in-°F = $0.1442$ W/m-K                    |  |

| Pressure                                                                  | 1 W/in-K = 39.3 W/m-K                              |  |

| 1 lb/in <sup>2</sup> (psi) = 6,894.76 N/in <sup>2</sup>                   | 1  cal/sec-cm-K = 418.4  W/m-K                     |  |

| 1 lb/ft <sup>2</sup> (psf) = 47.9 N/in <sup>2</sup> = 0.0069 psi          | Specific heat                                      |  |

| $1 \text{ MPa} = 10^6 \text{ N/m}^2 = 1 \text{ N/mm}^2$                   | 1  cal/g-°C = 4.17  W-sec/g-°C                     |  |

| 1 atm = 101325 Pa                                                         | 1 BTU/lb-°F = $4.1867$ W-sec/g-°C                  |  |

| $1 \text{ dyne/cm}^2 = 0.1 \text{ Pa}$                                    | Temperature                                        |  |

| $1 \text{ kg/cm}^2 = 14.22 \text{ psi}$                                   | 1°C = 33.8°F                                       |  |

| Force                                                                     | $0^{\circ}C = 273.15 \text{ K}$                    |  |

| 1 lb (force) = 4.448 N                                                    |                                                    |  |

| 1 gm (force) = 980.665 dyne                                               |                                                    |  |

| $1 \text{ dyne} = 10^{-5} \text{ N}$                                      |                                                    |  |

| 1 dyne = $2.248\times10^{-6}$ lb                                          |                                                    |  |

TABLE 10.3 Units and Conversion Factors

mal interface material may be required between the package and the board. A discussion of these materials can be found in Sec. 10.5.6.

#### 10.5 Packaging Materials

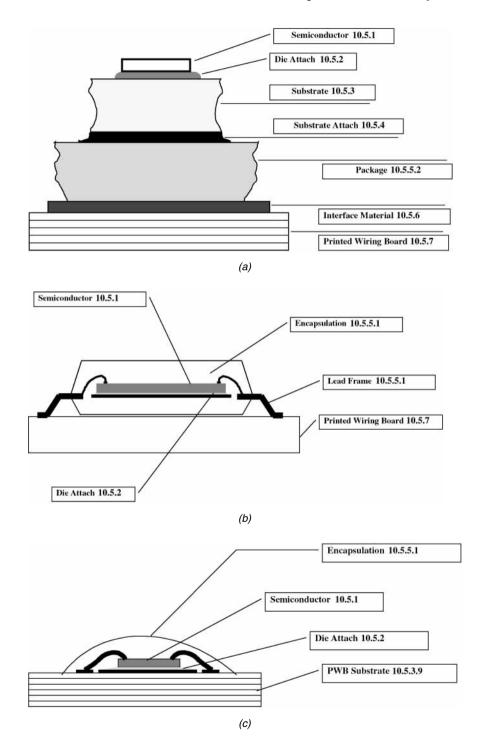

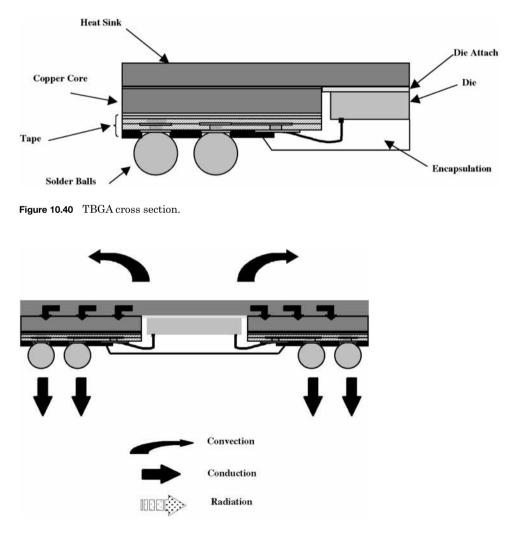

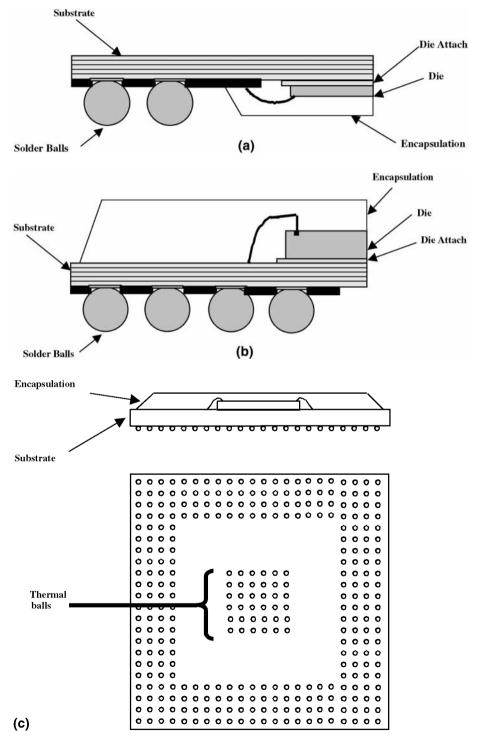

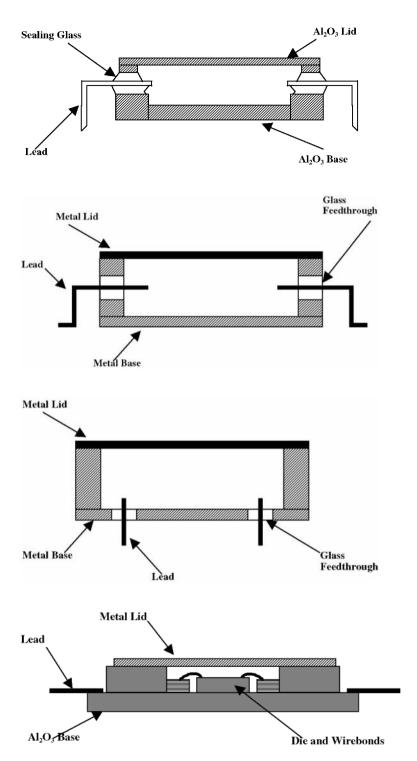

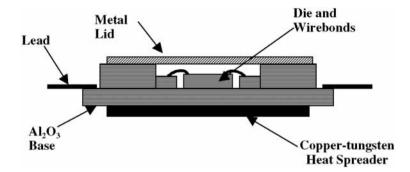

Figure 10.9 shows cross-sectional views of the various types of electronic packaging. The constituent materials used in each type of packaging are referenced to the applicable section of this chapter. **Thermal Management Materials and Systems**

Figure 10.9 Cross-sectional views of various package types: (a) hybrid microcircuit, (b) PEM, and (c) COB.

#### 10.5.1 Semiconductors

**10.5.1.1 Silicon and germanium.** The first transistors were fabricated with germanium (Ge) semiconductor material, which has a reasonably good thermal conductivity of 77 W/m-K. However, germanium suffers from an inherent leakage problem that limits the maximum operating temperature to the range of 90 to 120°C. Silicon transistors, invented at Texas Instruments in 1954, have maximum operating junction temperatures in the range of 150 to  $200^{\circ}$ C.<sup>9,10</sup> Forty years later, over 90 percent of all semiconductors are fabricated from silicon, which has a thermal conductivity of 150 W/m-K at 25°C.<sup>11</sup>

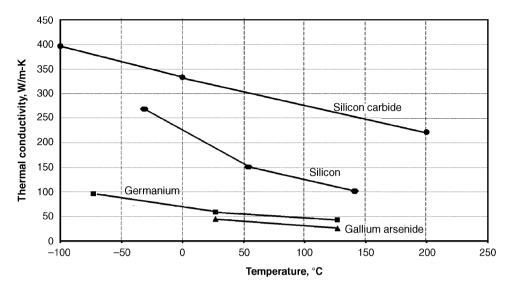

Table 10.4 lists the thermal conductivities of various semiconductor materials at 25°C. The variation of the thermal conductivity at temperature for several of these materials is shown in Fig. 10.10.

| Material          | Thermal conductivity<br>@ 25°C (W/m-K) |

|-------------------|----------------------------------------|

| Silicon           | 150                                    |

| Silicon germanium | 150                                    |

| Silicon carbide   | 155                                    |

| Gallium arsenide  | 45                                     |

| Indium phosphide  | 97                                     |

| Germanium         | 77                                     |

| Gallium phosphide | 133                                    |

| Gallium antimony  | 33                                     |

| Gallium nitride   | 16–33                                  |

| Indium arsenide   | 35                                     |

| Indium antimony   | 19                                     |

### TABLE 10.4 Thermal Conductivities of Semiconductor Materials<sup>3,13,23</sup>

**10.5.1.2 Compound semiconductors.** To obtain higher performance than silicon in either frequency or temperature range, compound semiconductors were developed using materials such as gallium arsenide, indium phosphide, indium arsenide, indium antimony, gallium phosphide, gallium antimony, and silicon carbide.

For high-frequency applications, typically starting at 1 GHz, gallium arsenide (GaAs) is used as the semiconductor material because of its higher mobility. Because of its high-frequency performance, gallium arsenide has found its way into a variety of applications ranging from cellular telephones to military radars. Other materials used for high-frequency operation include indium phosphide, indium arsenide, indium antimony, gallium phosphide, and gallium antimony.

Figure 10.10 Variation of the thermal conductivity of various semiconductor materials at temperature.

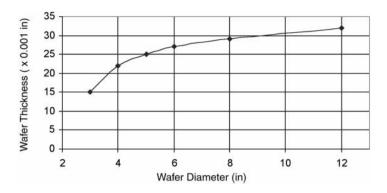

To achieve maximum high-frequency performance from gallium arsenide, circuit geometries are made extremely small. This increased power density, coupled with the lower thermal conductivity (35 W/m-K), makes the packaging of gallium arsenide a significant challenge to the physical designer. One technique commonly used with gallium arsenide to lower the thermal resistance is to thin down the wafers. Gallium arsenide chips are also thinned so as to reduce the impedance of through-hole vias from the top to the bottom of the chip. Typical thicknesses of gallium arsenide used in the microelectronic assemblies are 0.006 and 0.002 in.

A new compound semiconductor material, silicon-germanium (SiGe), is fabricated by selectively introducing germanium as a dopant into the base region of the transistor. The processing of silicon-germanium wafers is done using the same equipment as standard silicon. The resulting silicon-germanium material produces a semiconductor that offers comparable high-frequency performance to gallium arsenide at a significantly lower cost. An example of the high-frequency capability of the silicon-germanium process is IBM's recently demonstrated 210-GHz silicon-germanium transistor. The amount of germanium in silicon-germanium is small. Therefore, the thermal conductivity can be considered to equal that of silicon.<sup>15–17</sup>

Silicon carbide (SiC) is a compound semiconductor material that is finding its way into a variety of applications. With a wide band gap of 3.1 eV (versus 1.1 eV for silicon), heat does not readily disrupt the performance of silicon carbide semiconductors. In addition to the wide band gap, silicon carbide has a high thermal conductivity: 333 W/m-K at 25°C and 221 W/m-K at 200°C. As a result, silicon carbide semiconductors are being used in a variety of high-temperature applications. Silicon carbide has a high maximum electron velocity, which allows devices to operate at high frequencies.<sup>14,18,19</sup> Indium phosphide is a new compound semiconductor material being used for high-frequency electronic and optoelectronic devices with the potential of integrating both on a single chip. Indium phosphide's relatively high thermal conductivity of 97 W/m-K allows it to be used in high-power-density applications.<sup>20,21</sup>

Gallium nitride (GaN) is a developing semiconductor material with a wide bandgap that can effectively handle large amounts of power and operate at frequencies up to 40 GHz. While the thermal conductivity of gallium nitride is a low 16 to 32 W/m-K, it has a power density that is many times that of gallium arsenide and indium phosphide. Gallium nitride is finding applications such as power amplifiers in base stations.<sup>22,23</sup>

#### 10.5.2 Die attach materials

Except for flip-chip-attached devices, all die are bonded to the next assembly (the substrate or package) active area facing up with a die-bond adhesive. It is the die bond that absorbs the thermal mismatch between the die and the package or substrate. Thus, the die bond is susceptible to fatigue fracture. The adhesives fall into two categories, soft and hard. Soft adhesives include organics, polymers, and lead-based solders. Hard adhesives include gold-based eutectics (gold-silicon, gold-germanium, and gold-tin), silver-based solder (Sn 96), and silver-glass.

**10.5.2.1 Gold-silicon eutectic.** Eutectic die attachment is based on the gold-silicon eutectic point at 370°C. In this process, the die is mechanically scrubbed with a gold-silicon perform on a substrate or a ceramic package at temperatures between 390 and 450°C under a nitrogen shroud. On semiconductors with no backside metallization, the scrubbing breaks down the thin layer of silicon on the back of the chip and combines it with another metal, usually gold. For gold-backed semiconductors, the gold-silicon perform is reflowed and attaches the die to the underlying metallization. The resulting gold-silicon eutectic structure is approximately 0.001-in thick and has a thermal conductivity of 27 W/m-K.<sup>13</sup>

**10.5.2.2 Solders.** For semiconductors metallized with non-gold metals such as titanium-nickel-silver, other eutectic solders are used. These include gold-tin, with a eutectic temperature of 280°C; gold-germanium, with a eutectic temperature of 361°C; and Sn 96, with a eutectic temperature of 221°C. (Note that gold-tin, gold-germanium, and Sn 96 can be used with both gold-backed and non-gold-backed die.) Other solders used for die attach include a variety of lead-tin and indium-lead solders. The thermal conductivities of the various solders used as die attach adhesives are listed in Table 10.5.<sup>38</sup> Preforms of gold-tin, gold-germanium, and Sn 96 come in various thicknesses, starting at 0.001 in. Solder pastes, a mixture of solder particles and flux, are available for a number of solder alloys for use in dispensing, screen printing, and stencil-

| Solder         | Composition                                | Thermal conductivity<br>@25°C (W/m-K) | CTE,<br>(ppm/°C) |

|----------------|--------------------------------------------|---------------------------------------|------------------|

| Gold-silicon   | 96.85 Au, 3.15 Si                          | 27                                    | 12.3             |

| Gold-tin       | 80 Au, 20 Sn                               | 57                                    | 15.9             |

| Gold-germanium | 88 Au, 12 Ge                               | 44                                    | 13.4             |

| Sn 10          | 90 Pb, 10 Sn                               | 36                                    | 27.9             |

| Sn 96          | $3.5\mathrm{Ag},96.5\mathrm{Sn}$           | 33                                    | 30.2             |

| Sn 62          | $2\mathrm{Ag},36\mathrm{Pb},62\mathrm{Sn}$ | 42                                    | 27               |

| Sn 63          | 37 Pb, 63 Sn                               | 51                                    | 25               |

| Sn 60          | 40 Pb, 60 Sn                               | 29                                    | 27               |

| Indium-lead    | 30 Pb, 70 In                               | 38                                    | 28               |

| Indium-silver  | 3 Ag, 97 In                                | 73                                    | 22               |

TABLE 10.5 Thermal Properties of Solders<sup>38</sup>

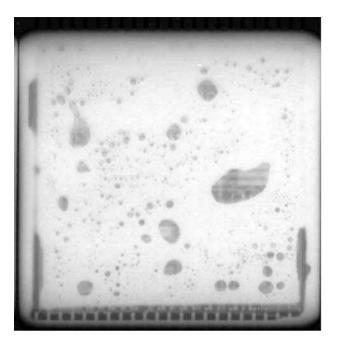

ing. When solder pastes are used, there is a possibility of creating voids in the die attach as a result of flux entrapment. This is discussed in Sec. 10.6.2.

The lack of plastic flow in hard adhesives leads to high stresses in the silicon chip as a result of the CTE mismatch between the substrate/package and the die. $^{24}$

**10.5.2.3 Silver-glass.** As semiconductors grew in complexity from medium scale integration (MSI) to large scale integration (LSI), and in size past 0.2 inches square with power densities exceeding 32 W/in<sup>2</sup> (5 W/cm<sup>2</sup>), the eutectic die attach process became inadequate. Assembly houses could not provide high enough void-free attachment in volume to meet the thermal resistance requirements. In addition, the CTE mismatch between silicon at 3.6 ppm/°C and 92 percent alumina packages at 7.2 ppm/°C was introducing significant reliability-decreasing stresses.<sup>13</sup>

Silver-glass die attach materials were developed to provide void-free die attach with low thermal resistance. Composed of approximately 60 percent silver flake, 20 percent glass, and 20 percent organic binders that are burned off completely during the processing, silver-glass has a thermal conductivity ranging from 60 to 80 W/m-K, depending on the manufacturing formulation. This is an order of magnitude higher than epoxies. See Table 10.6 for details. Silver-glass is applied to the semiconductor package or to the substrate with dispensing equipment to provide an after-firing bond line of 0.002 in minimum.<sup>28</sup> Typical processing temperatures for silver-glass die attach are 400 to  $420^{\circ}$ C.<sup>26</sup> Owens has reported that there was no cracking of die when attached with silver-glass.<sup>28</sup> The same die, when attached eutectically, was exhibiting cracking. The thermal properties of several silver-glass compositions are listed in Table 10.6.

| Material  | Thermal conductivity<br>@25°C (W/m-K) | CTE (ppm/°C) |

|-----------|---------------------------------------|--------------|

| QMI3555R  | >80                                   | 16           |

| QMI2419MA | >60                                   | 21           |

| DM-3030   | 70                                    | 19.7         |

| JM4720    | 78.3                                  | 17           |

TABLE 10.6 Thermal Properties of Silver-Glass<sup>25–27</sup>

**10.5.2.4 Organic adhesives.** Polyimides, cyanate esters, and epoxies filled with precious metals are widely used for die attach in all types of packaging. Their ease of application and low processing temperatures have made them the die attach material of choice in many applications. These organic adhesives are typically filled with a metal to provide the required electrical and thermal conductivity. Silver is the most common fill material. In selected applications, gold and copper are used as the fill material. To improve the thermal conductivity of organic adhesives, some manufacturers add electrically insulating materials such as boron nitride, aluminum nitride, alumina, and CVD diamond as fillers.

For single-chip packaging, dispensing and stamping are the preferred methods of application of organic adhesives. In multichip applications, the adhesives are typically screen printed or dispensed. With the proper dispensing pattern, void-free die attach can easily be achieved.

Many polymers come as a preform in which a carrier is impregnated with epoxy. Typical carrier materials are fiberglass and Kapton.<sup>\*</sup> These preforms provide an extremely uniform material thickness. Preforms with thicknesses as thin as 0.0015 in are available for use in die attach. Thicker preforms, up to 0.006 in thick and unfilled, are typically used for substrate attachment in multichip applications. These are discussed in Sec. 10.5.4.

Polymers are grouped into two categories—thermoplastics and thermosets. Thermoplastics, made from ground cured resins and mixed with fillers and a solvent, are capable of softening or melting when heated and return to a solid when cooled. Because of the presence of the cured resins, thermoplastics do not require any subsequent curing. Thermosets, typically referred to as *epoxies*, are uncured or partially cured. They do not have the reversible phase-change behavior of thermoplastics. The thermal conductivity of both thermoplastics and thermosets is a first-order function of the type and amount of filler material. When used for die attach, the typical filler material is silver. Because thermoplastics do not require a cure, the bond line they form is dense and void-free, with a resulting higher thermal conductivity. Thermosets, which require a cure, have small voids caused by shrinkage during curing that result in a lower-density bond line and thus a lower thermal conductivity.<sup>31,32</sup>

<sup>\*</sup> Kapton is a registered trademark of DuPont.

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com) Copyright © 2004 The McGraw-Hill Companies. All rights reserved. Any use is subject to the Terms of Use as given at the website.

Polyimide and cyanate ester adhesives, both metal-filled and unfilled, are more thermally stable than epoxy adhesives and are used for higher-temperature applications such as furnace sealing. Epoxies have a maximum temperature range of 175°C to 250°C, depending on their composition. Polyimides, stable to 400°C to 500°C, have thermal conductivities close to 0.16 W/m-K.<sup>19</sup> Silver-filled cyanate esters, stable to over 400°C have thermal conductivities of approximately 1 W/m-K.<sup>33</sup> The thermal conductivities of polyimide and cyanate ester die attach adhesives are extremely low. However, because their thickness is on the order of 0.001 inch or less, the resultant thermal resistance of the die attach, while not low, is acceptable for low to medium power densities.

Thermoplastic and thermoset adhesives come in both a paste and a preform. The critical thermal parameters for both materials are the thickness of the die attach and its uniformity. The screen printing and dispensing processes can provide uniform bond lines. By definition, the preform provides a uniform thickness. Table 10.7 lists the thermal conductivities of various organic adhesives used for die attach.

#### 10.5.3 Substrates and metallizations

In all multichip applications and selected single-chip applications, the dice are attached to a substrate that provides interconnection as well as electrical isolation from the package. This substrate material can be a ceramic, a metal with insulating dielectric, or an organic. Ceramic substrate materials include alumina, beryllium oxide, low-temperature cofired ceramic (LTCC), and aluminum nitride. Table 10.8 lists the thermal properties of inorganic substrates. In multilayer substrates, the dielectric material has a very large effect on the overall thermal resistance and is discussed below in detail.

Table 10.9 lists the thermal conductivities of various thick film substrate dielectric materials. Metal substrates include steel, copper, and aluminum with subsequent dielectric layers. Whereas the physical parameters that set the thermal resistance for a substrate are primarily the thermal conductivity of the base material and the dielectric material, the conductor material has a very important effect on the thermal resistance. The conductors, composed of various metals, when used as a plane or planes, serve to spread the heat and thus lower the thermal resistance. Therefore, in the subsequent discussion on substrate materials, the methods of metallizing will be presented with a focus on thermal conductivity.

Inorganic substrates, used for low-cost applications, are discussed in Sec. 10.5.7, Printed Wiring Boards.

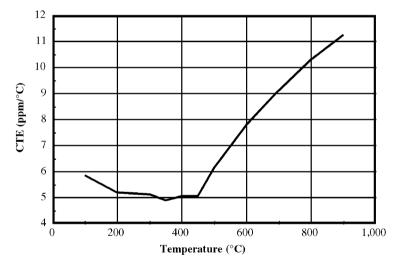

**10.5.3.1** Alumina. The most commonly used ceramic material in electronic packaging is alumina,  $Al_2O_3$ , or aluminum oxide. It is used both as a body of a hermetic package and as a substrate. The CTE of the 96 percent alumina, 6.3 ppm/°C (25 to 400°C),<sup>13</sup> closely matches that of silicon and several metal packaging alloys (Kovar and Alloy 42). This close match prevents differential stresses that can lead to mechanical failure.

#### 10.24 Chapter 10

| Manufacturer     | Material   | Material type                 | Thermal<br>conductivity<br>@25°C<br>(W/m-K) | Comments       |

|------------------|------------|-------------------------------|---------------------------------------------|----------------|

| Ablestik         | 84-1LMISR4 | Thermoset-conductive          | 2.5                                         |                |

| Ablestik         | 84-1LMIT   | Thermoset-conductive          | 5.9                                         |                |

| Ablestik         | ECF561     | Thermoset- conductive         | 1.6                                         |                |

| Emerson & Cuming | 5025E      | Thermoset-conductive          | 3.5                                         |                |

| Emerson & Cuming | ECF561     | Thermoset-conductive          | 1.6                                         |                |

| AI Technology    | TC8750     | Thermoset-conductive          | 6.5                                         |                |

| Epoxy Technology | T6116      | Thermoset-conductive          | 1.5                                         |                |

| Epoxy Technology | H20E       | Thermoset-conductive          | 2.0                                         |                |

| DIEMAT           | 6030HK     | Thermoset-conductive          | 60                                          |                |

| Hysol            | KO120      | Thermoset-conductive          | 2.8                                         |                |

| Ablestik         | 84-3J      | Thermoset-nonconductive       | 0.8                                         |                |

| Emerson & Cuming | 561K       | Thermoset-nonconductive       | 0.9                                         |                |

| Emerson & Cuming | 506        | Thermoset-nonconductive       | 0.9                                         |                |

| Emerson & Cuming | 5020K      | Thermoset-nonconductive       | 0.7                                         |                |

| AI Technology    | TK78759    | Thermoset-nonconductive       | 11.6                                        | Diamond filled |

| AI Technology    | TP8260     | Thermoplastic-conductive      | 6.5                                         |                |

| AI Technology    | TP7155     | Thermoplastic-conductive      | 1.6                                         |                |

| DIEMAT           | 4030LD     | Thermoplastic-conductive      | 15                                          |                |

| Ablestik         | 2600K      | Thermoplastic/thermoset blend | 20.0                                        |                |

| AI Technology    | TP7095     | Thermoplastic-nonconducting   | 1.6                                         |                |

| AI Technology    | TP7755     | Thermoplastic-nonconducting   | 1.8                                         |                |

| AI Technology    | TP7459     | Thermoplastic-nonconducting   | 11.5                                        | Diamond filled |

| Ablestik         | 71-1       | Polyimide                     | 2.1                                         |                |

| Ablestik         | JM2000LB   | Cyanate Ester                 | 1.8                                         | @ 121°C        |

| Ablestik         | JM2500     | Cyanate Ester                 | 1.1                                         | @ 121°C        |

#### TABLE 10.7 Thermal Properties of Organic Adhesives<sup>27,29,30,45,86</sup>

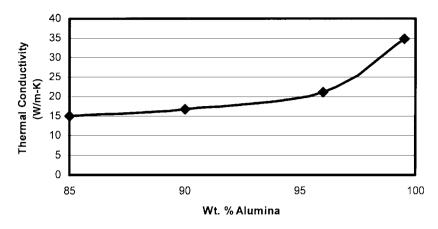

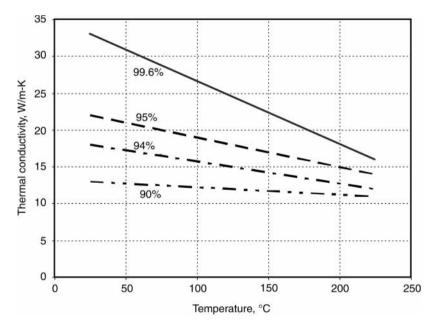

The thermal conductivity of alumina ranges from 12 to 35 W/m-K, depending on the purity. The highest purity available, 99.6 percent alumina, is typically used for thin film applications and has a thermal conductivity of 34.7 W/m-K at 25°C. Ninety-six percent alumina, typically used with thick-film metallization, has a thermal conductivity of 21 W/m-K at 25°C. Figure 10.11 shows the measured thermal conductivity for various percentages of alumina. In addition to thermal conductivity varying with the percentage of alumina, it also varies with temperature variation as shown in Fig. 10.12.<sup>13,39</sup>

| Material name         | Thermal conductivity<br>@25°C (W/m-K) | CTE<br>(ppm/°C) |

|-----------------------|---------------------------------------|-----------------|

| Alumina 92%           | 17                                    | 7.2             |

| Alumina 96%           | 21                                    | 6.3             |

| Alumina 99.9%         | 30                                    | 7.4 (25–400°C)  |

| Beryllium oxide 99.5% | 248                                   | 6.4             |

| Aluminum nitride      | 170                                   | 4.2             |

| LTCC                  | 2.0-4.4                               | 4.5 - 8.0       |

| CVD diamond           | 1300-2000                             | 2.0             |

TABLE 10.8 Thermal Properties of Inorganic Substrates<sup>13,34</sup>

#### TABLE 10.9 Thermal Properties of Thick Film Dielectrics<sup>35–37</sup>

| Material name      | Application       | Thermal conductivity<br>@25°C (W/m-K) |

|--------------------|-------------------|---------------------------------------|

| DuPont dielectrics | Thick film glass  | 3.0                                   |

| 41010-25C          | Tape on substrate | 2.5 - 3.0                             |

| GPA98-047          | Steel substrates  | 4.3                                   |

Alumina can be metallized with refractory metallizations (e.g., tungsten or moly-manganese), thin films, thick films, direct copper plating, and direct bond copper. The use of ground or power planes in either substrate or package metallization can aid in spreading the heat.

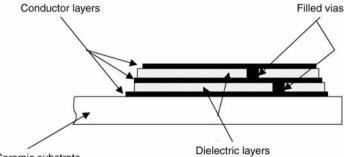

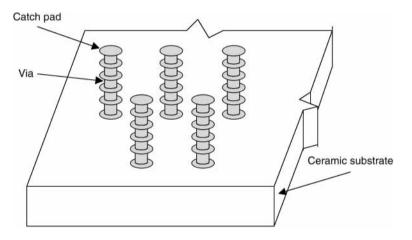

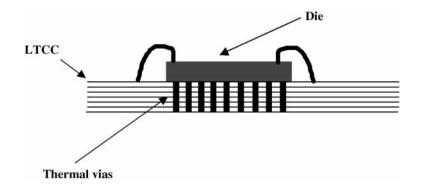

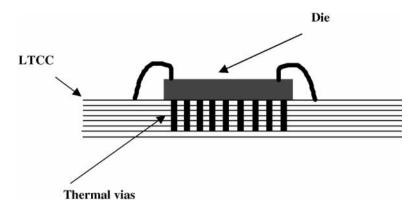

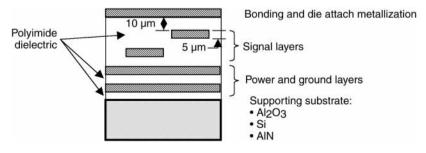

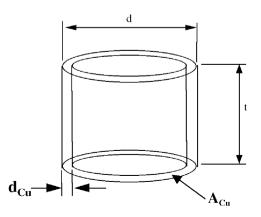

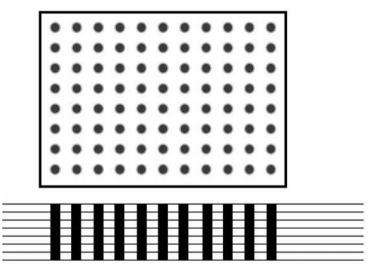

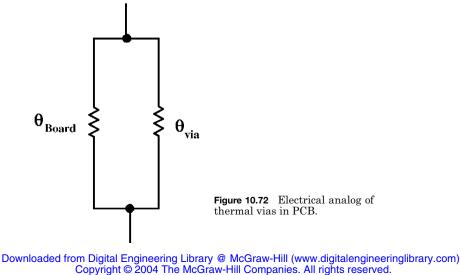

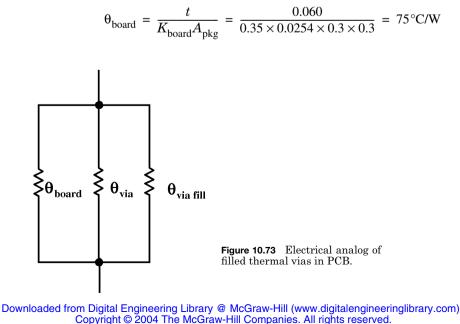

Multilaver thick films usually use screen-printed glass as the dielectric layers as depicted in the cross section shown in Fig. 10.13. This glass is both an electrical and a thermal insulator. The typical thermal conductivity of thickfilm glass is identical to that of LTCC, which is 3.0 W/m-K.<sup>40</sup> To improve the effective thermal conductivity of multilayer thick-films, the physical designer makes use of thermal vias. As shown in Fig. 10.14, thermal vias are a series of filled vias stacked upon each other in an array. The bottom of the stack is attached either to the ceramic substrate or to a plane. Thick-film conductor inks, whether they are gold, silver, or an alloy, are not pure metals. The inks consist of a functional material of metal, a solvent, a temporary binder, and a permanent binder. This permanent binder is used to tailor the CTE to that of the substrate and to aid in the adhesion to either the dielectric or the ceramic substrate. During firing, the solvent and temporary binders are burned out, leaving a conductor whose properties are no longer that of the pure metal functional material. In addition to altering the CTE, the permanent binder reduces both the electrical and thermal conductivity of the conductor. Typical fired thick-film conductors are 8 µm thick. If this conductor were pure gold, it

Figure 10.11 Effect of weight percent of Al<sub>2</sub>O<sub>3</sub> on thermal conductivity.

Figure 10.12 Variation of thermal conductivity of alumina at temperature.

would have a sheet resistivity of  $3 \text{ m}\Omega/\Box$ . The 5715 thick-film gold conductor material from DuPont Electronics specifies a sheet resistivity of less than  $5 \text{ m}\Omega/\Box$  for the same fired thickness.<sup>35</sup> The composition of via fill inks is slightly different from that of conductors. This allows the via fill to closely match the CTE of the dielectrics and, in the process, changes both the thermal and electrical conductivities. The sheet resistivity of DuPont Electronics' 5727 gold via fill material is  $15 \text{ m}\Omega/\Box$ . This is five times that of pure gold. There is also a drastic difference in the thermal conductivity of thick-film gold in comparison with pure gold. Thick-film gold via fill has a measured thermal con-

Ceramic substrate

Figure 10.13 Multilayer thick film dielectric cross section.

Figure 10.14 Portion of a thermal via array in multilayer thick film dielectric.

ductivity of 20.1 W/m-K (see Ref. 41), whereas pure gold has a thermal conductivity of 297 W/m-K.  $^{24}$

There are two key parameters in the design of thermal vias in thick films. The diameter of the via is determined by the filling process. If the diameter is too large, it will be difficult to fill with just one or two screen printings. The design of the spacing or pitch of the vias is a trade-off. Obtaining the maximum thermal conduction requires a high pitch or high density of vias. But a high pitch has two problems. First, it restricts routing of the signals. Even though via fill materials are designed to match the CTE of the dielectric, placing too many per unit area increases the effective CTE and puts the dielectric material into stress, which can result in cracking.<sup>8</sup>

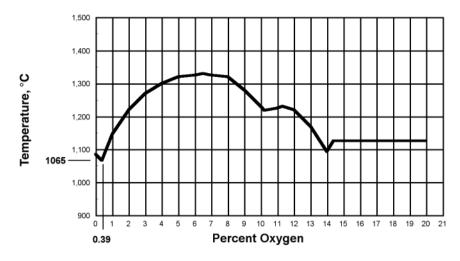

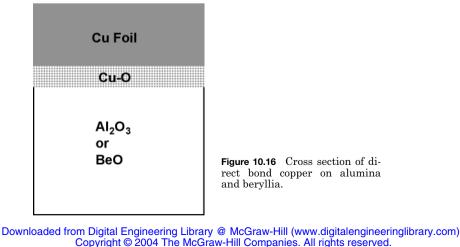

Direct bond copper (DBC) is a patented<sup>42</sup> process, originally developed at General Electric, in which copper is eutectically attached to oxygen-bearing ceramics such as alumina and beryllium oxide. As shown in the copper-oxygen phase diagram in Fig. 10.15, copper and oxygen have a eutectic point at 1065°C. At this point on the phase diagram, there is 0.39 percent oxygen. When copper is placed on the ceramic between 1065 and 1083°C (the melting

Figure 10.15 Copper-oxygen phase diagram.

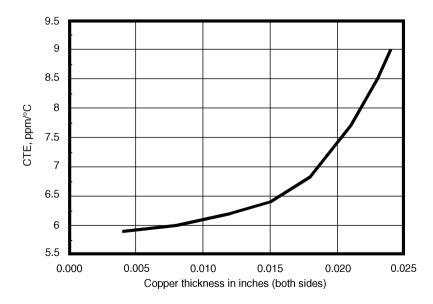

point of copper), the copper fuses with the ceramic. A cross section of direct bond copper is shown in Fig. 10.16. There is a thin layer of Cu-O between the copper and the ceramic. In microelectronics applications, the thickness of the copper foil can range from 0.001 to 0.020 in. Because copper has a CTE of 16.12 ppm/°C,<sup>43</sup> which is many parts per million higher than that of the ceramic, it can place the ceramic in tension and either warp it or cause it to crack. To prevent this, manufacturers of direct bond copper typically place equal amounts of copper on both sides of the ceramic. A curve for the equivalent CTE versus copper thickness for an alumina substrate with equal amounts of copper on each side is shown in Fig. 10.17.<sup>44</sup> Most DBC manufacturers recommend limiting the thickness of the copper on each side of the substrate as a percentage of the ceramic thickness to prevent warping and cracking of the ceramic.<sup>45</sup>

Any use is subject to the Terms of Use as given at the website.

Most applications of direct bond copper require it for its high electrical conductivity. Typical values of sheet resistivity are significantly less than 1 m $\Omega/\Box$ . An added benefit of DBC is its high thermal conductivity as a result of the excellent spreading capability of the copper. Nguyen has developed an equation for the equivalent thermal conductivity of direct bond copper substrates.<sup>47</sup>

$$K_{e} = \frac{\sum_{i=1}^{n} K_{i} t_{i}}{\sum_{i=1}^{n} t_{i}}$$

(10.26)

where  $K_e =$  equivalent thermal conductivity

$\vec{K_i}$  = thermal conductivity of each material  $T_i$  = thickness of each material

n = number of materials

**Example** Find the equivalent thermal conductivity of a direct bond copper substrate consisting of 0.010-in thick copper on each side of a 0.025-in thick beryllium oxide substrate.

- $K_{Cu} = 401 \text{ W/m-K}$

- $K_{BeO} = 248 \text{ W/m-K}$

- $t_{Cu} = 0.010$  in

- $t_{BeO} = 0.025$  in

Figure 10.17 Equivalent TCE vs. copper thickness for a 0.025-in alumina substrate with equal amounts of copper on each side.

The thicknesses of the copper and beryllium oxide are first converted to metric units.

- $t_{C\mu} = 0.010 \text{ in} \times 0.0254 \text{ m/in} = 2.54 \times 10^{-4} \text{ m}$

- $t_{BeO} = 0.025 \text{ in} \times 0.0254 \text{ m/in} = 6.35 \times 10^{-4} \text{ m}$

Using Eq. (10.26), the equivalent thermal conductivity  $K_e$  is calculated.

$$K_e = \frac{2.54 \times 401 \times 6.35 \times 10^{-4} \times 248 + 2.54 \times 10^{-4} \times 401}{(2.54 + 6.35 + 2.54) \times 10^{-4}} = 8.03 \text{ W/m-K} \quad (10.27)$$

An alternative material used for dielectrics in thick film multilayer circuits is *tape transfer dielectric*. The tape dielectric process is a patented process<sup>48</sup> in which layers of glass-ceramic tape are applied to a fired, dimensionally stable substrate in lieu of screen printing the dielectric. This process has several trade names—TTRAN, Tape-on-Substrate, and DITRAN. The purpose of using tape dielectric in lieu of screen printing fine lines (as narrow as 0.002 in). The thermal conductivity of the 41010-25C tape dielectric material from Electro Scientific Laboratories is 2.5 to 3.0 W/m-K.<sup>49</sup>

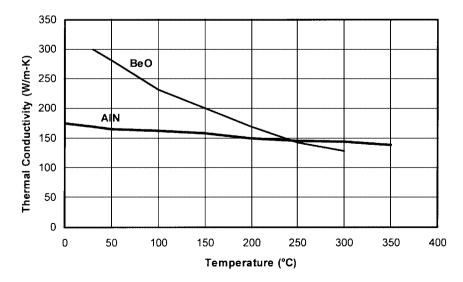

**10.5.3.2 Beryllium oxide.** Beryllium oxide, BeO, or *beryllia*, is often used when a high-thermal-conductivity substrate is required. At 25°C, beryllia has a thermal conductivity of 248 W/m-K,<sup>13</sup> a value ten times that of alumina. The thermal conductivity of BeO decreases with increasing temperature as shown in Fig. 10.18.<sup>19</sup>

Figure 10.18 Thermal conductivity variation of AlN (170 W/m-K) and BeO.

All beryllium compounds, including beryllium oxide, are toxic in powder form. However, in their solid form, they do not pose any health hazards. Therefore, operations such as grinding, cutting, laser trimming, and certain furnace operations need to be performed so that airborne beryllium oxide particles are not generated.

The dust of beryllium compounds causes *chronic beryllium disease* (CBD). It is also known as *berylliosis*, a disease whose symptoms include scarring and damage of lung tissue, shortness of breath, wheezing, and/or coughing.<sup>50</sup> The incidence of CBD requires three factors:

- 1. The individual must be allergic to beryllium. It is estimated that approximately 1 percent of the population is allergic to beryllium. Because those who are susceptible cannot be identified, 100 percent of the population must be protected.

- 2. The individual must be exposed to beryllium of a respirable size—less than 10  $\mu$ m. The only significant hazard associated with beryllium is inhalation. Airborne particles in excess of 10  $\mu$ m in size cannot penetrate the upper respiratory tract and enter the alveolar area of the lung.

- 3. The individual must be exposed to a sufficiently large concentration of airborne beryllium. There is no exact dividing line between safe and unsafe amounts. The recommended levels, which include guard bands, are  $2 \mu g/m^3$  average or 25  $\mu g$  peak.<sup>51</sup>

Because of the toxicity of beryllium oxide, several countries and some individual companies have banned its use.<sup>52</sup> Where beryllia is used, it must be clearly identified on the component and its shipping container.

Beryllia is commonly metallized with refractory metallization such as tungsten and moly-manganese, nickel, and gold plating. Other metallization methods include thin and thick films as well as direct bond copper. When multilayer thick films are used with beryllium, the thermal resistance must be broken down into two main parts—the ceramic and the glass/metal combination of the multilayers.

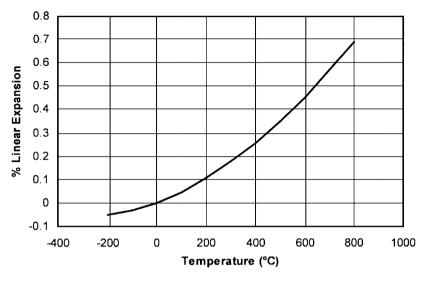

The CTE of 99.5 percent beryllia at 20°C is 6.4 ppm/°C, which is very close to that of alumina.<sup>13</sup> The variation of linear expansion of beryllia over the temperature range is shown in Fig. 10.19. This is a key parameter in mounting devices to the BeO or mounting the BeO to the next assembly.<sup>51</sup>

**10.5.3.3** Aluminum nitride. A high-thermal-conductivity alternative to beryllium oxide is aluminum nitride, AlN. Having a nominal thermal conductivity of 170 W/m-K at 25°C,<sup>13,55</sup> it is approximately seven times more thermally conductive than alumina. Aluminum nitride, with a room temperature CTE of 4.7 ppm/°C, is more closely matched to silicon (2.5 ppm/°C over the 20 to 100°C range)<sup>13</sup> than beryllium oxide or alumina. For many high-power applications, aluminum nitride is the substrate material of choice, as it is nontoxic. The thermal conductivity of aluminum nitride can have significant variation if the

Figure 10.19 TCE variation of beryllium oxide vs. temperature.

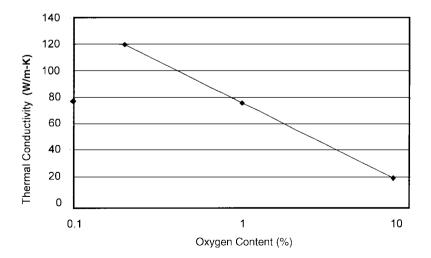

oxygen content varies. As shown in Fig. 10.20, a 0.2 percent change in oxygen content can have a 12.5 percent variation in thermal conductivity.

Both beryllium oxide and aluminum nitride have thermal conductivity degradation as the temperature increases. As shown in Fig. 10.18, the thermal conductivity of aluminum nitride becomes greater than that of beryllium oxide at temperatures greater than 240°C. Therefore, for operation at temperatures in excess of 240°C, aluminum nitride is the ceramic material of choice when high thermal conductivity is the selection criteria.<sup>19</sup>

Aluminum nitride can be metallized a number of ways. Single-layer thin film is a reliable metallization. Starting with a sputtered or evaporated adhe-

Figure 10.20 Copper-oxygen phase diagram.

sion layer, it can be plated with nickel and gold. Refractory metallization can also be used.

Aluminum nitride can be metallized using the classic thick film printing process using specially formulated inks. The oxide glasses in inks formulated for alumina are not chemically compatible with aluminum nitride. The CTE of glasses for dielectrics need to match those of the substrate. Because standard thick film inks are formulated for 96 percent alumina with a CTE of 6.3 ppm/ °C, they do not match the CTE of AlN at 4.2 ppm/°C.<sup>13</sup> In addition, the reactive bonding compounds in standard thick film inks in alumina are not effective in promoting adhesion to aluminum nitride substrates.<sup>56</sup> Several thick film ink manufacturers have developed inks that are compatible with aluminum nitride.<sup>57,58</sup>

Aluminum nitride can also be metallized using active metal brazing, a process that relies on an "active" (i.e., chemically reactive) constituent, usually titanium, to produce a wettable compound at the brazing interface.<sup>59</sup>

Aluminum nitride can be metallized with direct bond copper. However, the process used for oxide-bearing ceramics (alumina and beryllium oxide) must be modified to first grow an oxide of Al-O on the aluminum nitride. This oxygen layer thickness is on the order of angstroms. The copper oxide then fuses with this Al-O oxide. A cross section of direct bond copper on aluminum nitride is shown in Fig. 10.21. The effect of adding copper to both sides of aluminum nitride can be modeled in the same manner as described in Eq. (10.26).

One shortcoming of aluminum nitride is its decomposition to amorphous aluminum hydroxide when in contact with water at elevated temperatures. Aluminum nitride also reacts with cleaning solutions containing ammonia. The ammonia will etch the substrate and produce a porous surface finish that will lead to poor adhesion between metallization and the substrate.<sup>60</sup>

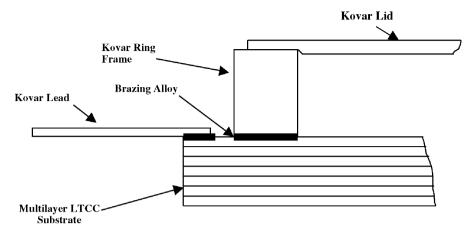

**10.5.3.4 Low-temperature cofired ceramic.** Low-temperature cofired ceramic (LTCC) is a thick film process technology commercialized by DuPont in 1985 and used for multilayer substrates and integral substrate-packages. The

| Cu Foil |                                                                               |

|---------|-------------------------------------------------------------------------------|

| Cu-O    |                                                                               |

| Al-O    |                                                                               |

| AIN     |                                                                               |

|         | Figure 10.21 Cross section of di-<br>rect bond copper on aluminum<br>nitride. |

|         |                                                                               |

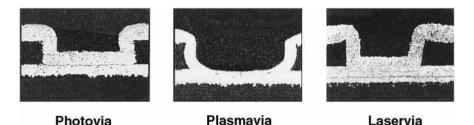

LTCC process starts off with "green" (unfired) ceramic tape that is a combination of glass and ceramic. It has a high glass content, allowing it to be fired at temperatures in the range of 850 to 950°C. This low firing temperature allows the LTCC to be metallized with low-resistivity gold, silver, and copper conductors. Vias, cavities, and registration holes are produced in the tape by mechanical drilling, punching, or laser ablation. Next, the individual layers are metallized using the classic screen-printing process. Vias are then filled. The individual layers are then collated, aligned, laminated, and fired in an air-fired furnace. During firing, the LTCC shrinks nominally 12.27 percent. The completed substrate is cut to size using either a mechanical or laser process.<sup>8,35</sup>

The thermal conductivity of LTCC ranges from 2.0 to 4.4 W/m-K, depending on the manufacturer and the particular formulation of the tape. See Table 10.10 for details. For all formulations of LTCC, the thermal conductivities are extremely low as a result of the high glass content (approximately 50 percent). To minimize the effect of the low thermal conductivity, physical designers can use cavities under high-power-density components, arrays of thermal vias, or a combination of both.<sup>36,40,61–63</sup>

| Material  | Manufacturer | Thermal<br>conductivity,<br>(W/m-K) | CTE (25–300°C),<br>(ppm/°C) |

|-----------|--------------|-------------------------------------|-----------------------------|

| 951       | DuPont       | 3.0                                 | 5.8                         |

| 943       | DuPont       | 4.4                                 | 4.5                         |

| 41110-70C | ESL          | 2.5 - 3.0                           | 6.4                         |

| 41020-70C | ESL          | 2.5 - 3.0                           | 7.4                         |

| A6M       | Ferro        | 2.0                                 | 7.0                         |

| A6S       | Ferro        | 2.0                                 | 8.0                         |

| TABLE 10.10 Therm | al Properties of LTCC <sup>36,40,61–63</sup> |

|-------------------|----------------------------------------------|

|-------------------|----------------------------------------------|

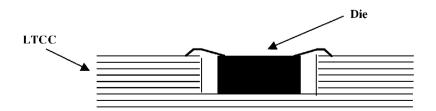

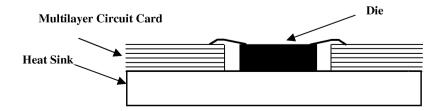

The number of layers of tape constituting an LTCC substrate can range from as few as 5 to as many as 50. To minimize the thermal resistance, the designer can place the high-dissipating component in a cavity as shown in Fig. 10.22. In this figure, the bottom of the die is electrically isolated from the back of the substrate with two layers of tape. The actual number of layers of tape under the cavity is a function of the area of the cavity and the strength of the

Figure 10.22 Isolated die in cavity under LTCC.

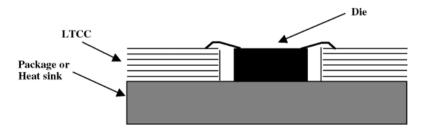

LTCC. For small devices (i.e., less than 0.1 in sq.), there can be only one or two layers of tape. For large devices, such as complex ASICS, there must be at least five layers of tape. When the back side of the die does not need to be electrically isolated and can sit on the package base or heat sink, the cavity can go through the entire LTCC substrate as shown in Fig. 10.23.

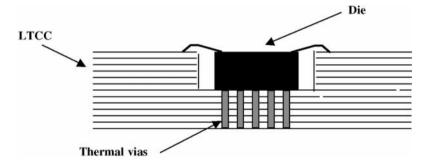

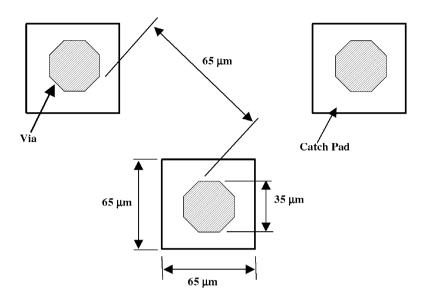

The use of thermal vias in LTCC is a standard method of improving the effective thermal conductivity. There can be an array of stacked vias going to the bottom of the substrate, as shown in Fig. 10.24, or to one layer above, as shown in Fig. 10.25. In the former case, the back side of the die does not need to be isolated from the bottom of the substrate. In the latter case, the bottom layer of the substrate provides the electrical insulation. Thermal vias can be used in conjunction with the die cavities discussed above. A cross section of a substrate with a die cavity and thermal vias is shown in Fig. 10.26.

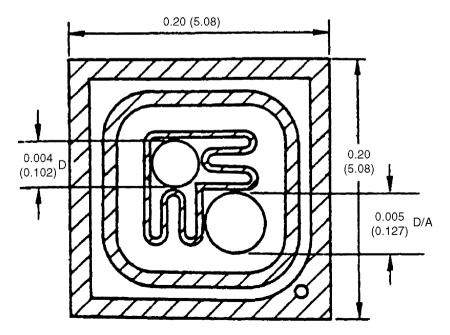

The density of the thermal vias and their diameter are typically set by the individual manufacturer of LTCC substrates with recommendations from the tape manufacturer. The via diameter is a function of the method used to fill the vias and the differential shrinkage of the via fill material and the LTCC material. An industry standard for via diameter is 0.006 in.<sup>8</sup> The density, or pitch, of the thermal vias is a function of the CTE of the via fill with respect to the CTE of the LTCC tape. The relative dimensions of a typical thermal via array are shown in Fig. 10.27.<sup>40,61</sup> For the industry standard 0.006-in diameter via, the spacing of the vias should be 0.018 in.

Figure 10.23 Cavity in LTCC with die directly attached to package or heat sink.

Figure 10.24 Thermal vias in LTCC.

Figure 10.25 Thermal vias in LTCC with electrically isolated die.

Figure 10.26 Cavity in LTCC with thermal vias.

Figure 10.27 Via dimensions in LTCC.

The LTCC manufacturer has a choice of gold, silver, or palladium silver inks for use as via fill materials. The silver inks are both electrically and thermally more conductive than the gold inks. DuPont<sup>35</sup> publishes electrical resistivity data for its via fill inks but does not give any thermal conductivity data. Licari<sup>8</sup> has data on average thermal resistance for very large (0.020-in dia.) gold and silver thermal vias that shows silver being 8 to 15 percent lower. Actual measured data are very limited. The measurements by Harshbarger<sup>64</sup> were used to calculate the thermal conductivity of 5718 gold via fill at 24.4 W/ m-K.<sup>41</sup>

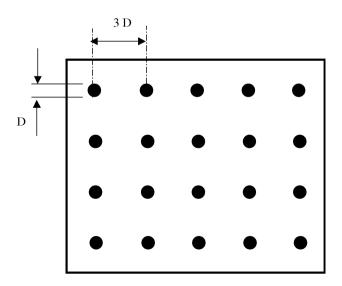

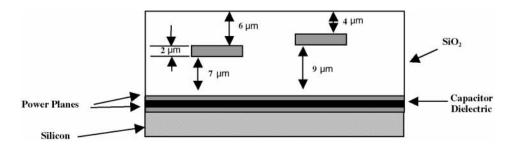

**10.5.3.5 Thin film multilayer substrates.** Thin film multilayer substrates are used to fabricate MCM-Ds (MCM-deposited). Many materials (alumina, silicon, aluminum nitride, and aluminum) are used as the supporting substrate and have been previously described. The difference is in the metallization and the insulating dielectric material. A cross-sectional view of a typical MCM-D substrate is shown in Fig. 10.28. Most MCM-D manufacturers use polyimide or other polymers as the dielectric in their thin film multilayer substrates. Internal metallization traces can be copper, gold, or aluminum. External (or top) metallization can be either aluminum or gold.<sup>8</sup>

The total thermal resistance of the thin film multilayer substrate consists of two resistances in series—the multilayer portion and the supporting material. The thermal conductivity of the thin film multilayer portion of the substrate is primarily determined by the low thermal conductivity of the polyimide. Typical values for the polyimide are in the range of 0.2 to 0.3 W/m-K (see Table 10.11).<sup>8,66</sup>

| Material        | Thermal conductivity<br>(W/m-K) |

|-----------------|---------------------------------|

| Polyimide       | 0.2–0.3                         |

| Silicon dioxide | 0.5 - 2.0                       |

| TABLE 10.11 | <b>Thermal Properties of Thin Film Dielectrics</b> |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

Figure 10.28 MCM-D substrate cross section with polyimide dielectric.

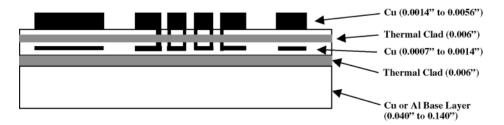

Some MCM-D manufacturers use silicon dioxide as the dielectric layer. A cross-sectional view of an MCM-D substrate with silicon dioxide dielectric is shown in Fig. 10.29. Silicon dioxide's thermal conductivity of 0.5 to 2.0 W/m-K is extremely low.<sup>3</sup>