Introduction to Packaging, Semiconductor Packaging, Chip Packages, PWB Design Max Marks: 30 Time: 1 hour

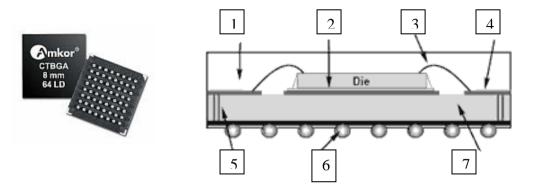

1. Label the arrowed sections in the figure below which is a cross-section of a CTBGA (ChipArray Thin Core BGA<sup>TM</sup>). (2 marks)

| 1 |  |

|---|--|

| 2 |  |

| 3 |  |

| 4 |  |

| 5 |  |

| 6 |  |

| 7 |  |

2. An automobile application requires a microcontroller for engine control. List the best option for the different package parameters (substrate, die attach, chip-package interconnection, package-PCB interconnection and encapsulation). Justify your choice, in brief.

(2 marks)

| Substrate material          |  |

|-----------------------------|--|

| Die attach                  |  |

| Die-package Interconnection |  |

| Package-PCB interconnection |  |

| Encapsulation               |  |

| Name of the Package >> >>>  |  |

3.

# NPTEL Video Course on "An Overview of Electronics Systems Packaging" Test 1 (mid-course) Syllabus: Modules 1-5

| Write the expansion for the following terms: | (any <u>TEN</u> ) |

|----------------------------------------------|-------------------|

| 1. SCSP                                      |                   |

| 2. LTCC                                      |                   |

| 3. OLGA                                      |                   |

| 4. PTH                                       |                   |

| 5. PSvfBGA                                   |                   |

| 6. QFN                                       |                   |

| 7. KGD                                       |                   |

| 8. PLCCH                                     |                   |

| 9. TSV                                       |                   |

| 10. COB                                      |                   |

| 11. SQFPH                                    |                   |

| 12. VTSOP                                    |                   |

| 13. CUEBGA                                   |                   |

| 14. T <sup>2</sup> BGA                       |                   |

| 15. FBGA-PoP                                 |                   |

|                                              | (5                |

4. IC Packaging efficiency is defined as the <u>ratio of IC size to package size</u>. Indicate in increasing order, the packaging efficiency for the following packages: WLP, BGA, DIP, SIP, PGA, QFP, MCM. Give a brief reasoning for your chosen order.

(2 marks)

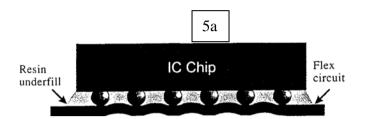

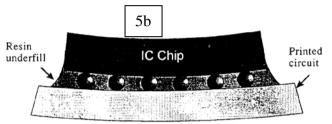

5. Figure 5a shows a flip chip with underfill on a flexible FR-4 base and the behaviour of the system under thermal load. Figure 5b shows a flip chip with underfill on a rigid FR-4 base and the behavior of the system under similar thermal load. Very briefly discuss both situations and indicate the preferred configuration (<u>5a or 5b or any other</u>) for high reliability and enhanced thermal cycling capabilities. (3 marks)

6. Match the following: (any <u>SIX</u>) (3 marks)

| Column A             | Column B          | ANSWERS |

|----------------------|-------------------|---------|

| 1. CCGA              | a. 183°C          | 1 =     |

| 2. Underfill         | b. Surface finish | 2 =     |

| 3. Eutectic Tin-Lead | c. epoxy polymer  | 3 =     |

| 4. VIP               | d. COB            | 4 =     |

| 5. Ni-Au             | e. CTE mismatch   | 5 =     |

| 6. Microvia          | f. 90:10 / Sn-Pb  | 6 =     |

| 7. Solder Mask       | g. 45 deg routing | 7 =     |

| 8. Glob top          | h. BGA            | 8 =     |

| 9. Mitring           | i. HDI            | 9 =     |

7. Comment on the following: (write in the space provided) (*Draw a pencil sketch where required*)

(8 marks) (ANY <u>FOUR</u>)

a. SOC (System on Chip) Vs SIP (System in Package).

b. Aspect Ratio of a Printed Wiring Board.

c. Ceramic CGA Vs Ceramic BGA.

d. ILB and OLB in a TAB attachment process.

e. Thermal vias for a PWB with BGAs (**OR**) Anti-pad Design for PWBs.

f. Solder reflow process Vs Conductive Adhesive bonding

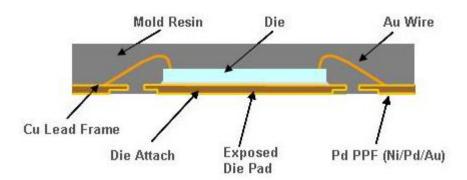

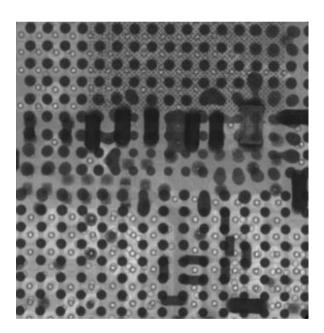

8. (a) <u>Identify/Name the package</u> illustrated below.

Answer: \_\_\_\_\_

(b) <u>Identify the defect</u> in the X-ray photograph below of a BGA solder joint.

Answer: \_\_\_\_\_

(5 marks)