Review PCB (PWB) Kinded Civait Bans Die Printed Wiring Board KGJ-Knomfood Rinted Civit Board Abembly Die (PCBA) L Singulated die active device , 2nd level package Wafer organic (plastic) inoganic (ceramic) Wafer fab (fabriation) > fint level packaging

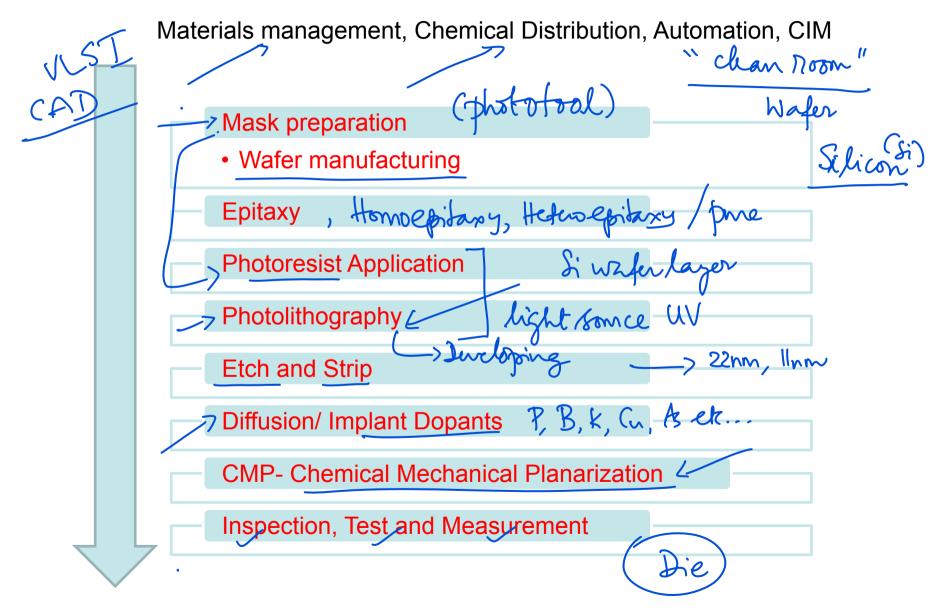

# Fabrication overview: Front-end

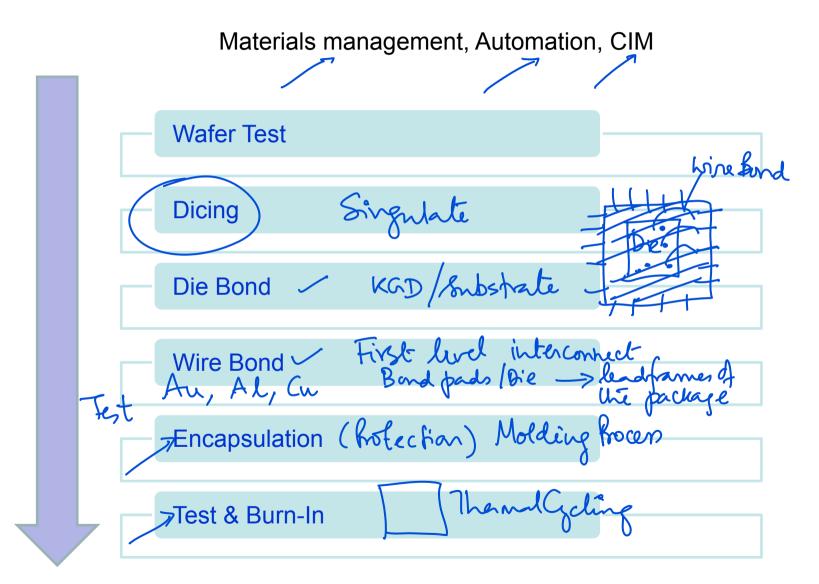

## Test, Assembly & Packaging :Back-end

#### Some Basics

- Semiconductor has resistivity lying between that of conductor and insulator

- It establishes its conduction properties through a complex quantum mechanical behaviour within a periodic array of semiconductor atoms.

- The resistivity is proportional to the free carrier density and this can be changed widely by doping different atomic species.

- Some dopants establish electron carrier density (n-type) and some establish hole carrier density (p-type).

- Electric fields enable electric switching between a conducting state and a non-conducting state. (carrier transport)

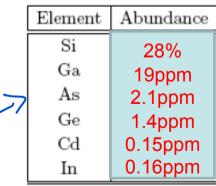

- Group IV elements: Ge, Si, C and Sn;

- Si is the most commonly used because of its abundance on earth.

Periodic Table

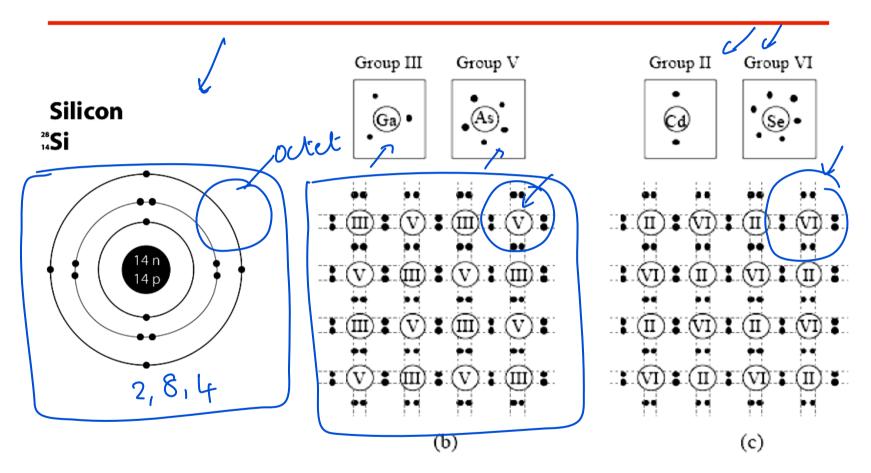

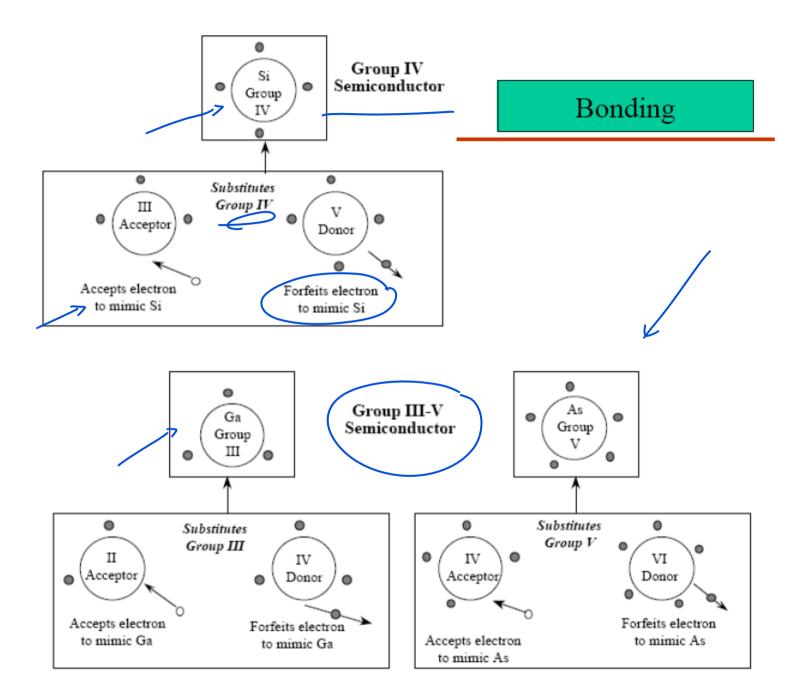

#### Formation of Semiconductor crystals

Bonding arrangements of atoms in semiconductor crystals. (a) Elemental semiconductor such as silicon. (b) Compound III-V semiconductor such as GaAs. (c) Compound II-VI semiconductor such as CdS.<sup>e</sup>

Transport and Mobility of electrons or holes

<u>Electron mobility</u> of semiconductors is used to describe the relation between the drift velocity of electrons or holes in a solid material or electrons/ions in a gas in an applied electric field.

### Unit cm<sup>2</sup>/V.s

Strongly dependant on impurities and dopants. The conductivity of the semiconductor is dependant on the mobility of the dominant charge carrier.

Typical electron mobility of GaAs at 300K is ~9000 cm2/V.s Si at 300K is ~1400 Ge at 300K is ~4000

## Making the Wafer

A seed crystal is suspended in a molten bath of silicon

- It is slowly pulled up and grows into an ingot of silicon

- The ingot is removed and ground down to diameter

• The end is cut off, then thin silicon wafers are sawn off (sliced) and polished

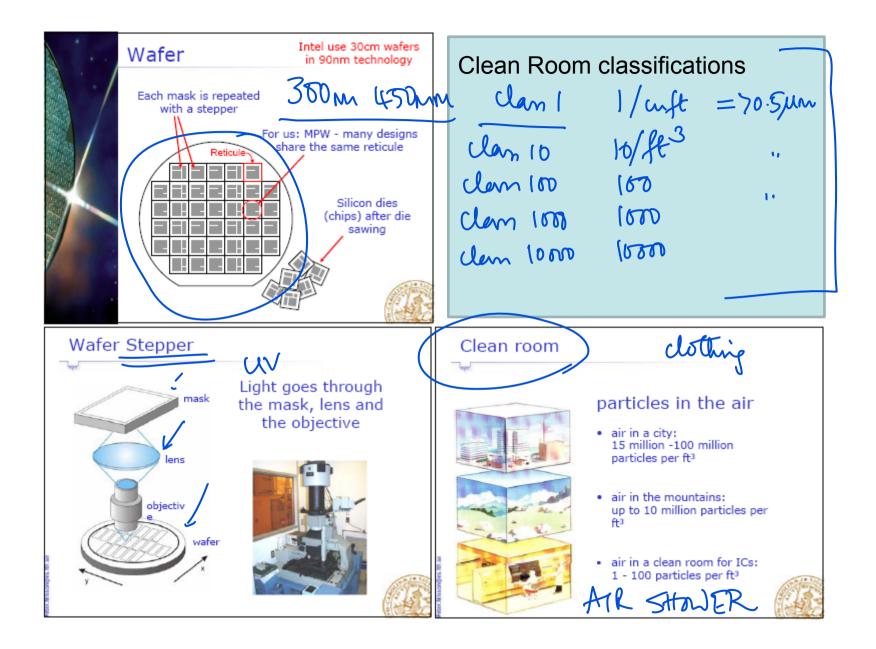

• For example, in a 8" wafer about 500 devices/ chips can be accommodated by design. They are rectangular in shape

• Wafers are processed typically in batches of 25 (lot)

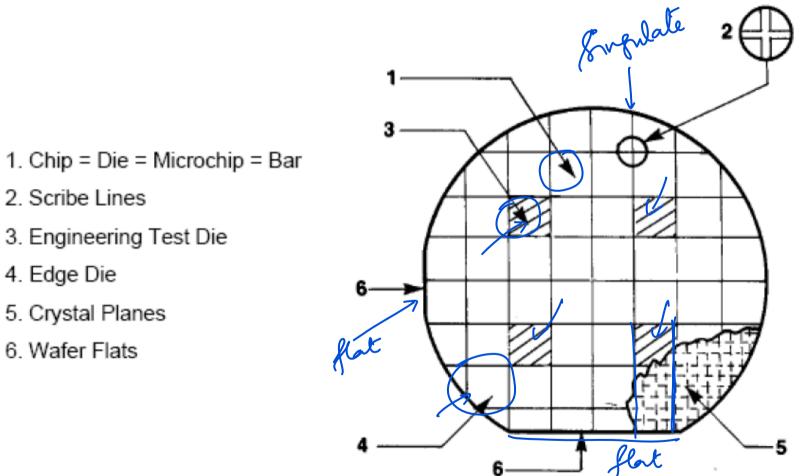

#### Wafer Terminology

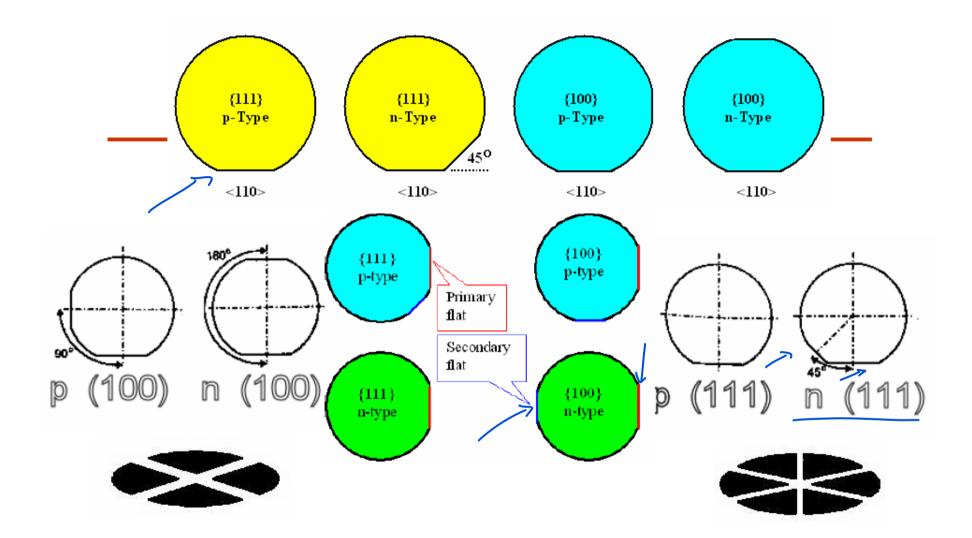

Wafers have **flats**, and the flats told you two things: The doping type of the wafer (**n**- or **p**-type)

The orientation of the wafer: {100} or {111}

Wafer processing Wet cleans **Photolithography** Ion implantation (in which dopants are embedded in the wafer creating regions of increased (or decreased) conductivity) Dry etching Wet etching Plasma ashing Thermal treatments Rapid thermal anneal Furnace anneals Thermal oxidation Chemical vapor deposition (CVD) Physical vapor deposition (PVD) Molecular beam epitaxy (MBE) Electrochemical Deposition (ECD). See Electroplating Chemical-mechanical planarization (CMP) (Polishing) Wafer testing (where the electrical performance is verified) Wafer backgrinding (to reduce the thickness of the wafer so the resulting chip can be put into a thin device like a smartcard or PCMCIA card.)

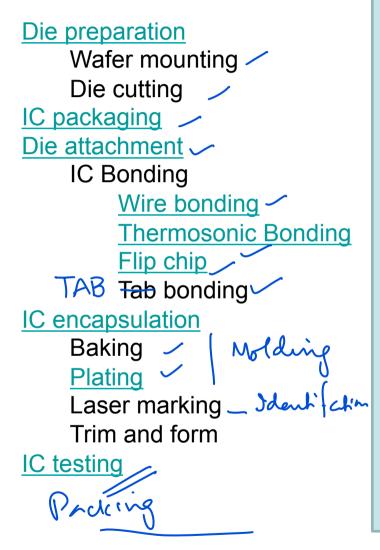

Plastic or ceramic packaging involves mounting the die, connecting the die pads to the pins on the package, and sealing the die.

Tiny wires are used to connect pads to the pins. In the old days, wires were attached by hand, Wine but now purpose-built machines perform the task.

Traditionally, the wires to the chips were gold, leading to a "lead frame" (pronounced "leed frame") of copper, that had been plated with solder, a mixture of tin and lead. Lead is poisonous, so lead-free "lead frames" are now mandated by ROHS.

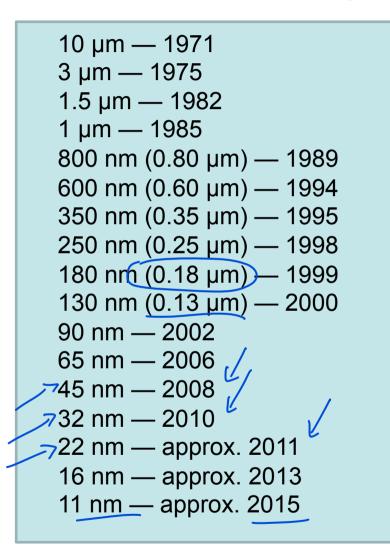

#### Semiconductor manufacturing processes

día Wafer sizes are 300mm, 450mm larger waters digs

Now, you will see a short video clip titled Sand-to-Silicon. This video is reproduced with written permission from Intel