Continuing..

## \*\*PRINTED WIRING BOARD TECHNOLOGIES\*\*

## IBM's Surface Laminar Circuit

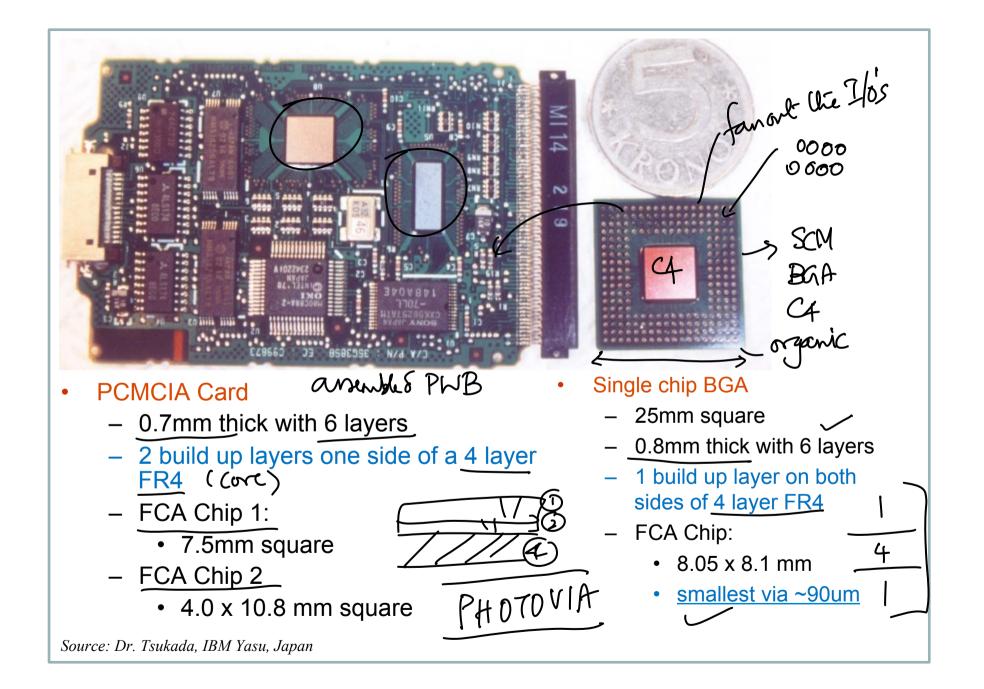

- Surface Laminar Circuit<sup>™</sup>: "An Organic Packaging Solution"

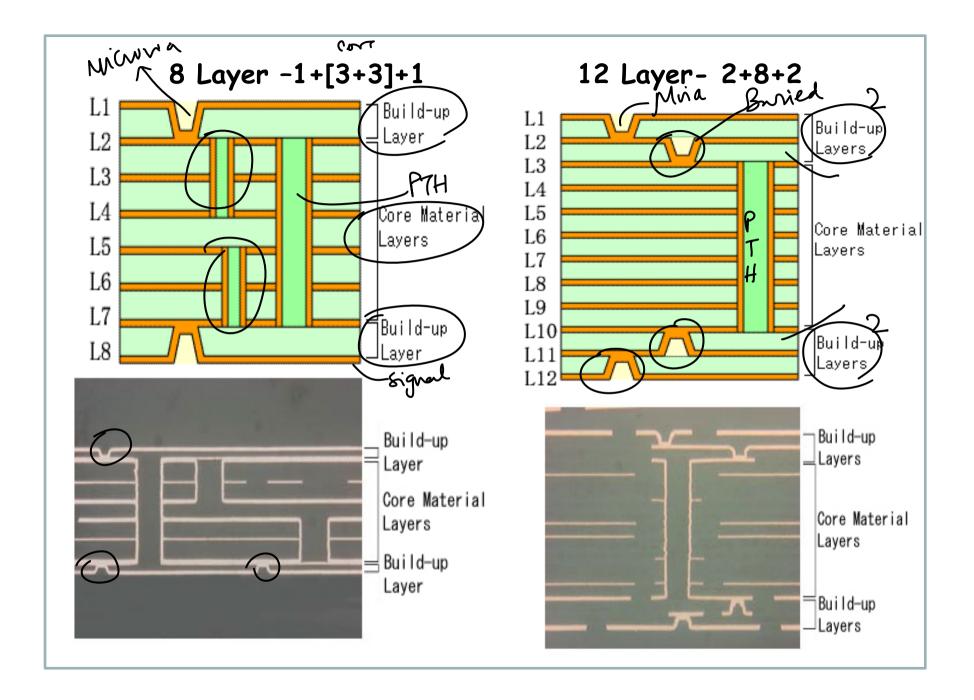

- SLC structure has two major parts

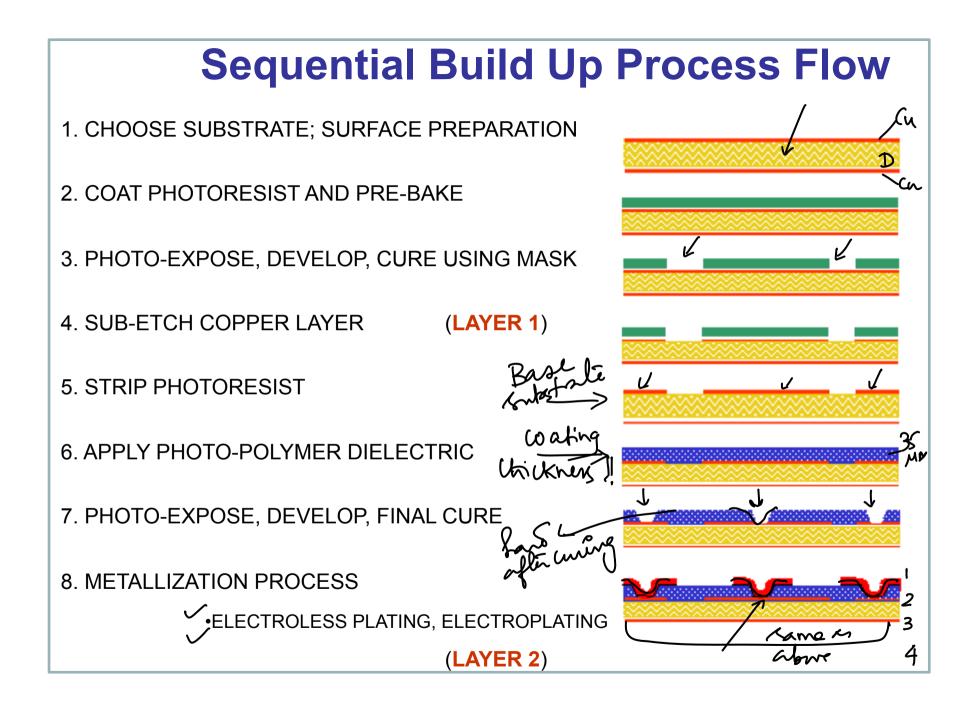

FR 4 substrate and

SLC layer built up (SBU technology)

- It is a methodology to have a PCB as a MCM-L and use existing PCB technologies

# Features

- High density

- 1mil via

- 1mil line and space

~1998-Production

- SMT pads on blind photo via

- More design freedom, routing capability

- Ability to accommodate <u>flip chip</u> and bare die; hence classifies under MCM-L//

- Used currently in video camcorders and telecommunication products

| characteristic                     | photo-liquid         | photo-film     | laser-RCC       | Laser-MP    | plasma             |

|------------------------------------|----------------------|----------------|-----------------|-------------|--------------------|

| dielectric cost                    | medium/high          | high           | high            | medium/high | <br>high           |

| via size (lab)                     | 50µm 🗸               | 100µm          | 75µm            | 100µm       | 100µm              |

| line width                         | 75                   | 75             | 100             | 100         | 75                 |

| line space                         | 75                   | 75             | 100             | 100         | 85                 |

| via diameter in production         | 125                  | 125            | 100             | 175         | 100                |

| max via layers                     | 3×2                  | 1×2            | 1×2             | 8           | 4                  |

| dielectric<br>thickness            | 40-80                | 60–80          | 60              | 100–250     | 50                 |

| dielectric<br>thickness<br>control | difficult            | good           | good            | good        | good               |

| dielectric her                     | 3.8                  | 3.8            | 3.8             | 3.5         | 3.5 <              |

| glass transition temperature       | 130°C                | 170°C          | 170°C           | 170°C       | 170–200°C          |

| process issues                     | pinholes             | conformability | conformability( | via filling | via shape          |

| process issues                     | adhesion             | adhesion       | hole cleaning   |             | non-uniform<br>via |

| process issues                     | thickness<br>control |                | m Chu           |             | slow process       |

|                       | Process                                            | Company    | Material                 | Lines/Spaces             | Via/Land                                     | Via Process<br>Diameter |

|-----------------------|----------------------------------------------------|------------|--------------------------|--------------------------|----------------------------------------------|-------------------------|

| D                     | V-Multi                                            | NEC        | Epoxy Film               | 80-50/<br>80-50 μm       | 100/250 µm                                   | Photo                   |

| IB                    | SS                                                 | Ibiden     | Epoxy Film               | 75-50/<br>75-50 μm       | 150-100/<br>250-150 μm                       | Photo                   |

| AI                    | LIVH                                               | Matsushita | Aramid Epoxy             | 60/90                    | 150/300 µm                                   | Laser                   |

| Et<br>Ro              | PERL (Plasma<br>Etched<br>Rdistribution<br>Layers) | Packard    | Epoxy film PI/<br>Aramid | 75/50 μm and<br>75/50 μm | 125-90/250-1<br>65 μm>                       | Plasma<br>Plasma/Laser  |

|                       | uild-up<br>ıbstrate                                | Fujitsu    | Ероху                    | 40/40 µm                 | 90/140 µm                                    | Photo                   |

| VI                    | B-2                                                | Victor     | Ероху                    | 10-95/100-75<br>μm       | 200-100/µm                                   | Photo                   |

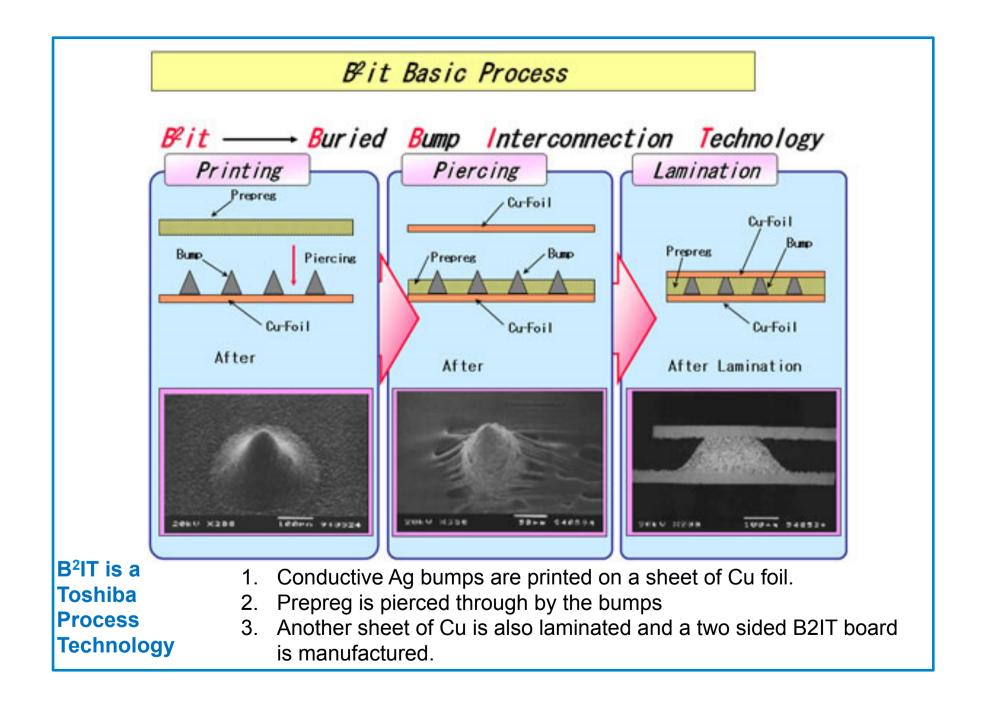

| <b>B</b> <sup>2</sup> | 2 <b>IT</b>                                        | Toshiba    | BT Laminate              | 90/90 µm                 | 200/300 µm                                   | Paste/Bump              |

|                       | ulti-Layer<br>uild-Up                              | Shinko     | Multiple                 | 40/40 µm                 | 50/110 µm                                    | Laser/Photo             |

|                       | LC (Surface<br>aminar<br>ircuit)                   | IBM Yasu   | Epoxy Liquid             | 75/50 μm anD             | 125-90/250<br>65 μm                          | Photo va                |

| Hi                    | itavia                                             | Hitachi    |                          | 100/100                  | 200/500                                      |                         |

| Vi                    | athin .                                            | Sheldahl   | PI                       | 50/37.5 μm               | 60-25/140-75<br>μm &<br>85/50/200-16<br>5 μm | Laser                   |

| Vi                    | ia <b>Ply</b>                                      | CTS        | PI/Aramid                | 75/75 µm                 | 125/125 µm                                   | Photo                   |

| TI                    | LPS                                                | Ormet      | PI                       | 50/50 µm                 | 25/200 µm                                    | Photo                   |

|                       | YCOstrate                                          | Dyconex    | PI                       | 100/125 μm               | 75/300 µm                                    | Plasma                  |

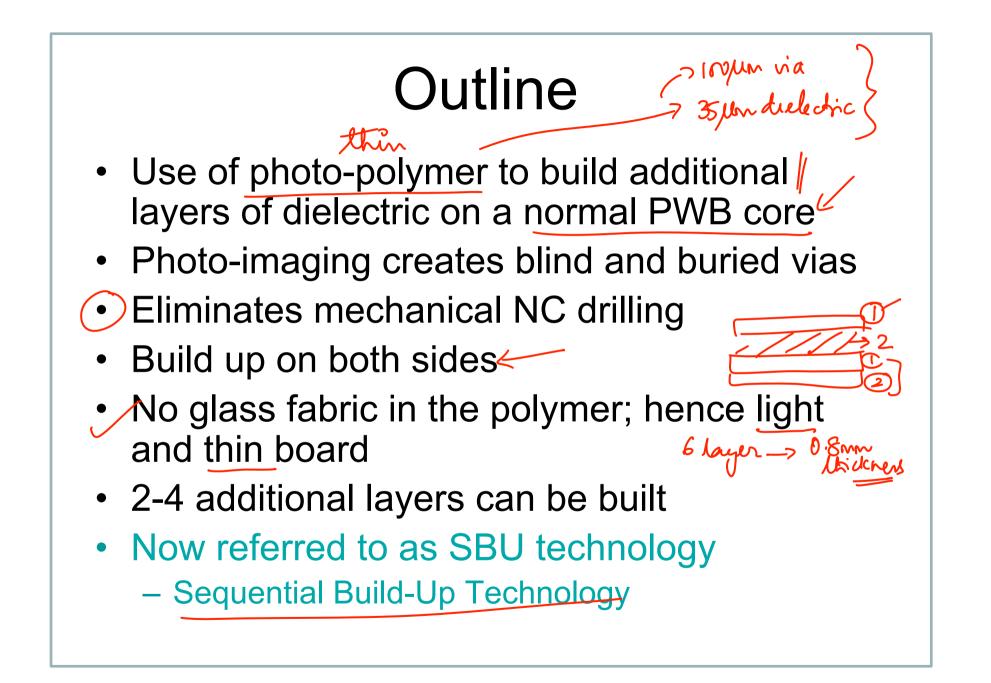

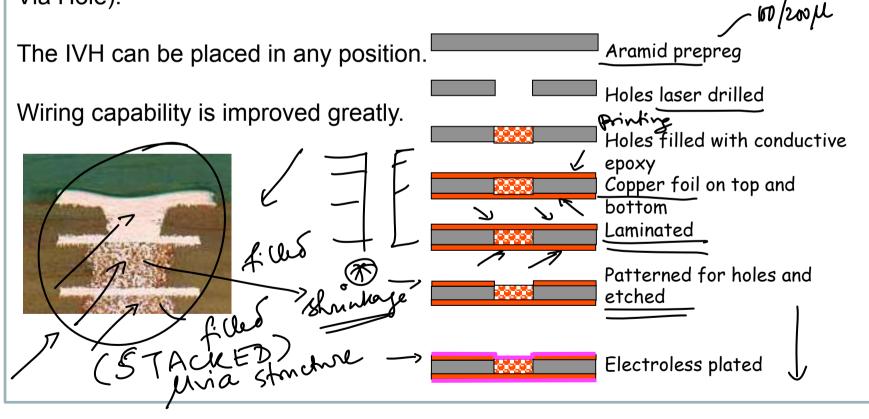

### ALIVH Technology- an SBU methodology

ALIVH boards (Any Layer Interstitial (inner) Via Hole) needs no throughhole.

This is because any two layers are electrically connected by IVH (Interstitial Via Hole).

#### Via in Pad Plated thorough hole (PTH) is filled by epoxy resin and plated by Cu as lid. Via in Pad structure can save surface area for wiring enabling the PTH pad to be able to mount SMT devices Flow property of conductive epoxy or other resin crucial for minimal shrinkage and electrical contact between layers. Minimum PTH diameter is 0.15mm, aspect ratio can be 8-10. SMD/BGA (DS no fling Provides a flat coplanar surface for component attachment More traces on PCB escaping devices through rout channels Increased component density due to absence of periphery vias Potential EMI benefits due to lower inductance Thermal dissipation (either at the lead joints or under devices by means of heat pipes No via plugging by soldermask required at the component locations